# TBM Field Engineering Theory of Operation

This information is furnished in accordance with requirements of Contract FA64WA-5223 and is subject to clause 24 thereof entitled "Reproduction and Use of Technical Data" which provides for its use, reproduction or disclosure by the Government for Governmental purposes.

# PREFACE

This manual presents those aspects of the IBM 9020E Display Channel Processor (DCP) which can be understood only in terms of the total system and its environment. It is intended for use by both students and trained maintenance personnel. The manual is divided into nine chapters as follows:

Chapter 1, Introduction, provides an overview of the 9020E System in terms of the tasks it must perform and the requirements it must meet.

Chapter 2, System Description, provides a brief description of each element and unit in the system.

Chapter 3, Interface Lines, describes the interfacing between system elements/units and defines each interface line.

Chapter 4, Configuration Control, explains the hardware and software implementation provided for the dynamic control of system configuration.

Chapter 5, Storage Addressing, describes the storageaddressing scheme and the address-translation capability of the 9020E System.

Chapter 6, Multisystem Operation, describes those system capabilities which are involved in operation of the system with more than one active computing element. These capabilities include: direct control, interrupts, shared storage, and reconfiguration.

Chapter 7, System Monitoring, describes the hardware facilities which permit the program to monitor system operation for malfunctions and abnormal conditions.

Chapter 8, Malfunction Handling, describes error recording, logout, and the manner in which each individual element/unit responds to malfunctions and abnormal conditions.

Chapter 9, System Initialization, describes resets, initial program load (IPL), and restarting operation from the system standpoint.

Two appendices are also provided. Appendix A, Comparative Instruction Listing, shows the valid op codes for the CE (in 360 mode and normal 9020 mode) and for the IOCE (in IOCE-processor mode and normal mode). Appendix B, System/360 Mode of Operation, describes the differences in system operation resulting from operation in the 360 mode.

The following manuals are to be used in conjunction with this introduction manual:

#### General

| A27-2734  | 9020D/E Principles of Operation, SRL       |

|-----------|--------------------------------------------|

| SFN-0105  | 9020D/E Power Controls and Distribution,   |

|           | FETOM                                      |

| SY22-2799 | Solid Logic Technology Power Supplies,     |

|           | FEMI                                       |

| SY22-2800 | Solid Logic Technology Packaging, FETOM    |

| SY22-2798 | Solid Logic Technology Component Circuits, |

|           | FEMI                                       |

|           |                                            |

#### First Edition (July, 1970)

This manual has been prepared by IBM Product Publications, Kingston, N.Y.

©Copyright International Business Machines Corporation, 1970

ii (7/70)

# 7201-02 Computing Element

| SFN-0201 | 7201-02 Computing Element, FETOM |

|----------|----------------------------------|

| SFN-0202 | 7201-02 Computing Element, FEMDM |

| SFN-0203 | 7201-02 Computing Element, FEMM  |

#### 7231-02 I/O Control Element

ā

1

| ZZ22-2865    | 7231-02 I/O Control Element, FETOM          |

|--------------|---------------------------------------------|

| Y22-2866     | 7231-02 I/O Control Element, Control Panel, |

|              | FETOM                                       |

| Z22-2867     | 7231-02 I/O Control Element, FEMDM          |

| ZZ22-6823    | 7231-02 I/O Control Element, FEMM           |

| (See 7231-02 | FETOM preface for additional references.)   |

#### 7251-09 Storage Element

| SFN-0301 | 7251-09 Storage Element, FETOM |

|----------|--------------------------------|

| SFN-0302 | 7251-09 Storage Element, FEMDM |

| SFN-0303 | 7251-09 Storage Element, FEMM  |

# 7289-04 Display Element

| SFN-0401 | 7289-04 Display Element, FETOM |

|----------|--------------------------------|

| SFN-0402 | 7289-04 Display Element, FEMDM |

| SFN-0403 | 7289-04 Display Element, FEMM  |

# 7265-03 Configuration Console

| SFN-0501 | 7265-03 Configuration Console, FETOM |

|----------|--------------------------------------|

| SFN-0502 | 7265-03 Configuration Console, FEMDM |

| SFN-0503 | 7265-03 Configuration Console, FEMM  |

# 2701-01 Data Adapter Unit

| SFN-0901 | 2701-01 Data Adapter Unit, FETMM |

|----------|----------------------------------|

| SFN-0902 | 2701-01 Data Adapter Unit, FEMDM |

# Channels

| SY22-2826 | System/360 Model 50, Selector Channel,          |

|-----------|-------------------------------------------------|

|           | Common Channel, FETOM                           |

| SY22-2827 | System/360 Model 50, Multiplexer Channel, FETOM |

#### Channel-to-Channel Adapter

Y22-6806 Channel-to-Channel Adapter, Model 6006A, FETMM Y22-6807 Channel-to-Channel Adapter, Model 6006A, FEMDM

# 2803A (SLT) Tape Control Unit

| SY32-5001 | 2803A Tape Control Unit, FETOM     |

|-----------|------------------------------------|

| SY32-6002 | 2803A Tape Control Unit, FEMM      |

| Y22-6781  | 2803, 2803A Tape Controls for 9020 |

|           | System, FETOM                      |

# Magnetic Tape Units

| SY22-2819 | Magnetic Tape Units 2401, 2402, 2403     |

|-----------|------------------------------------------|

|           | Models 1-6; 2404 Models 1-3; FETOM       |

| SY22-2854 | 2401-2402, 2403 Models 1-3 Magnetic Tape |

|           | Unit; 2403 Models 1–3 and 2803 Model 1   |

|           | Tape Control; FEMDM                      |

| SY22-6631 | Magnetic Tape Units 2401, 2402, 2403     |

|           | Models 1–3; FEMM                         |

# 1052 Adapter

(Refer to 7201-02 Computing Element, FETOM, Appendix C.)

#### 1052 Printer/Keyboard

| S225-3179 | 1052 Printer/Keyboard and 1053 Printer,<br>FETMM       |

|-----------|--------------------------------------------------------|

| S225-3353 | Selectric <sub>®</sub> I/O Keyboardless Printer, FETOM |

| S225-3207 | Selectric <sub>®</sub> I/O Keyboardless Printer, FEMM  |

#### 2821 Integrated Control Unit

| SY24-3359 | 2821 Integrated Control Unit, FETOM    |

|-----------|----------------------------------------|

| SY24-3503 | 2821 Integrated Control Unit, FEMDM    |

| SY24-3383 | 2821 Integrated Control Unit, FEMM     |

| SY25-3479 | 2821 Control Unit, Two-Channel Switch, |

|           | FETOM                                  |

| SY24-3508 | 2821 Control Unit, Two-Channel Switch, |

|           | FEMDM                                  |

#### 2540 Card Read/Punch

| SY31-0081 | 2540 Card Read/Punch, FEMI  |

|-----------|-----------------------------|

| SY31-0168 | 2540 Card Read/Punch, FEMDM |

| SY31-0082 | 2540 Card Read/Punch, FEMM  |

# 1403 Printer

| S225-6492 | 1403 Printers, | FEMI |

|-----------|----------------|------|

| S225-6493 | 1403 Printers, | FEMM |

#### Legend:

SRL

- FETOM - Field Engineering Theory of Operations Manual

- FETMM - Field Engineering Theory and Maintenance Manual FEMI

- Field Engineering Manual of Instruction

- FEMDM - Field Engineering Maintenance Diagrams Manual

- FEMM - Field Engineering Maintenance Manual

- Systems Reference Library

# CONTENTS

| CHAPTER 1 INTRODUCTION                       | 1-1      |

|----------------------------------------------|----------|

| System Requirements                          | 1-2      |

| Function of DCP System Elements              | 1-3      |

| 9020E DCP System Structure                   |          |

| •                                            |          |

| CHAPTER 2 SYSTEM DESCRIPTION                 | 2-1      |

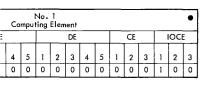

| IBM 7201-02 Computing Element                | 2-1      |

| Interfacing                                  | 2-1      |

| Internal Organization                        | 2-4      |

| Address Translation                          |          |

| Storage Control Interface (SCI)              | 2-4      |

| Instruction Fetch and Operand Prefetch Logic |          |

| Instruction Execution Logic                  |          |

| Interruption and Exceptional Conditions      | 2-6      |

| External Interface                           |          |

| Manual Controls and Maintenance Features     |          |

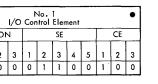

| IBM 7231-02 I/O Control Element              |          |

| Interfacing                                  |          |

| Internal Organization                        |          |

|                                              |          |

| Common Logic Unit                            |          |

| MACH (Maintenance and Channel) Storage       |          |

| Multiplexer Channel                          | 2-10     |

| Selector Channel                             |          |

| IOCE I/O Operations                          | 2-11     |

| IOCE-Processor Operations                    | 2-11     |

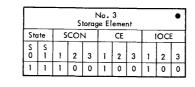

| IBM 7251-09 Storage Element                  |          |

| Interfacing                                  |          |

| Storage Addressing                           | 2-13     |

| Storage Protection                           | 2-13     |

| Internal Organization                        | 2-13     |

| Storage-Switching Unit                       | 2-13     |

| Storage Section                              | 2-14     |

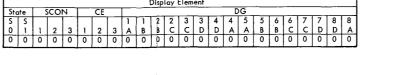

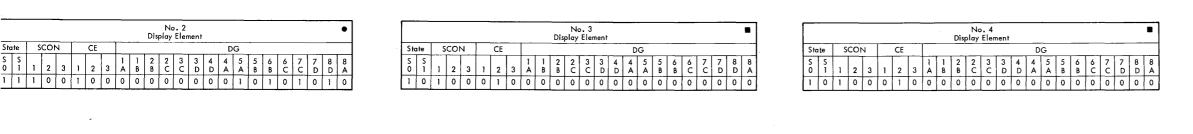

| IBM 7289-04 Display Element                  | 2-14     |

| Interfacing                                  |          |

| DE Storage Addressing                        | 2-16     |

| Storage Protection                           |          |

| Internal Organization                        | 2-17     |

| IBM 7265-03 Configuration Console            | 2-18     |

| System Console Function                      | 2-20     |

| Operator Intervention                        | 2-20     |

| Program-Addressable Areas of Console         | 2-20     |

| Hardware-Generated Indications               | 2-20     |

| Hardware-Generated Indications               | 2-20     |

| Reconfiguration Function                     | 2-20     |

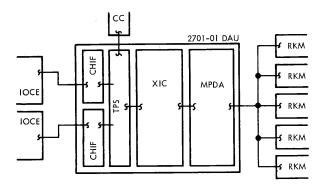

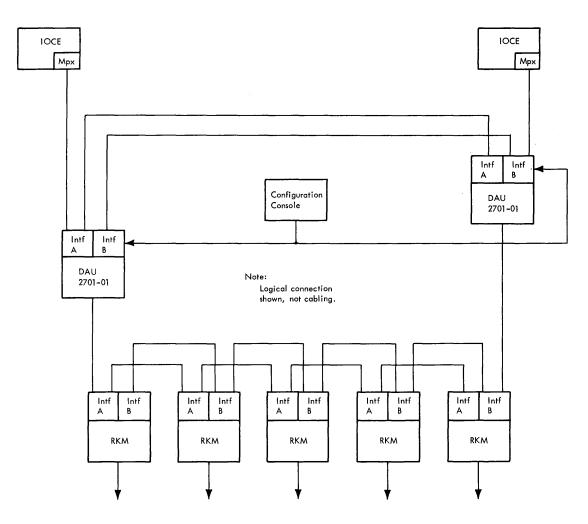

| IBM 2701-01 Data Adapter Unit                | 2-22     |

|                                              | 2-23     |

| Internal Organization                        | · · 2 23 |

| Channel Interface (CHIF)                     | · · 2 23 |

|                                              | · · 2-23 |

|                                              |          |

|                                              |          |

| · · · · · · · · · · · · · · · · · · ·        | 2-23     |

| IBM 2803-01 Tape Control Unit                | 2-24     |

|                                              | ~ 1      |

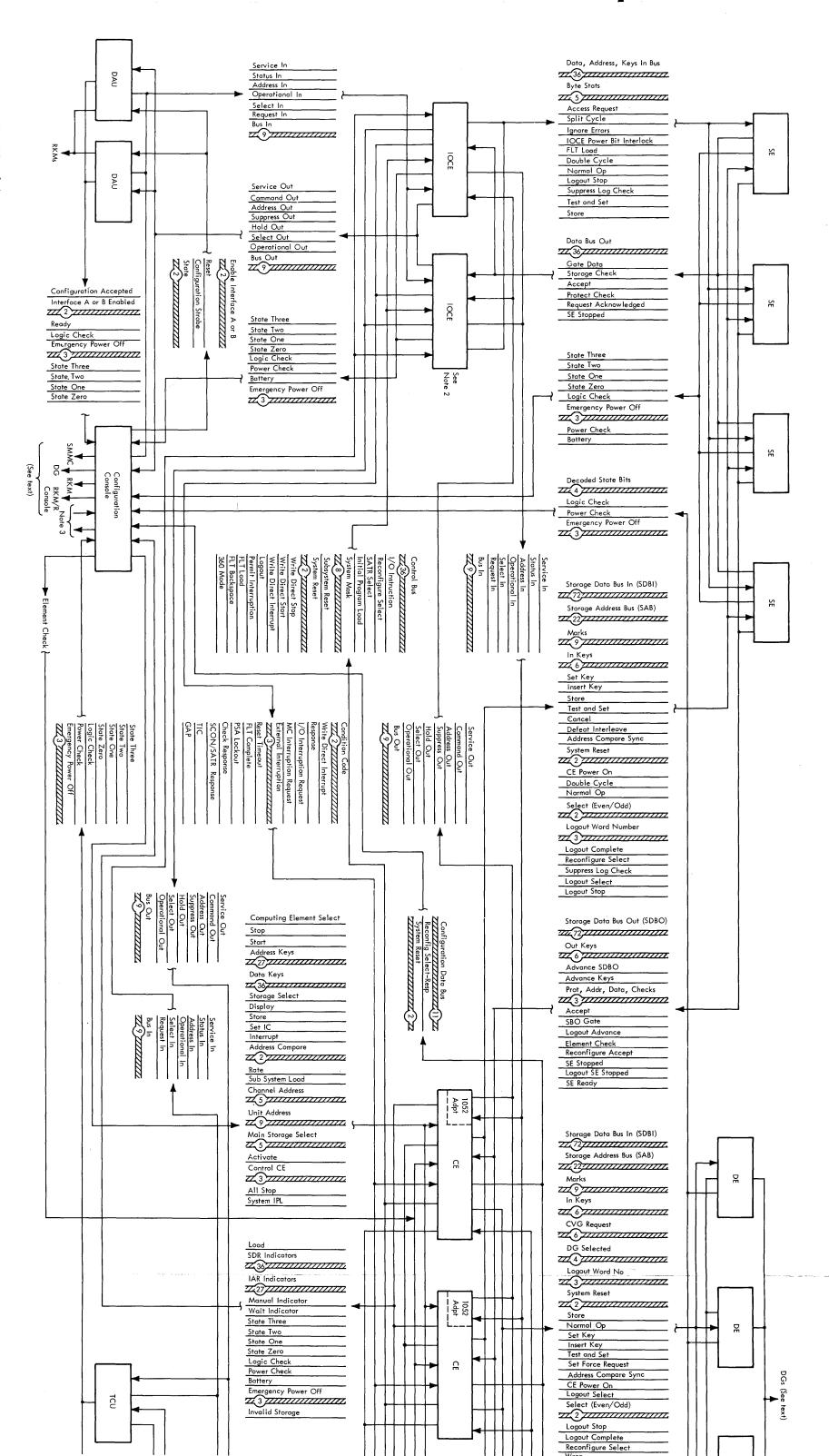

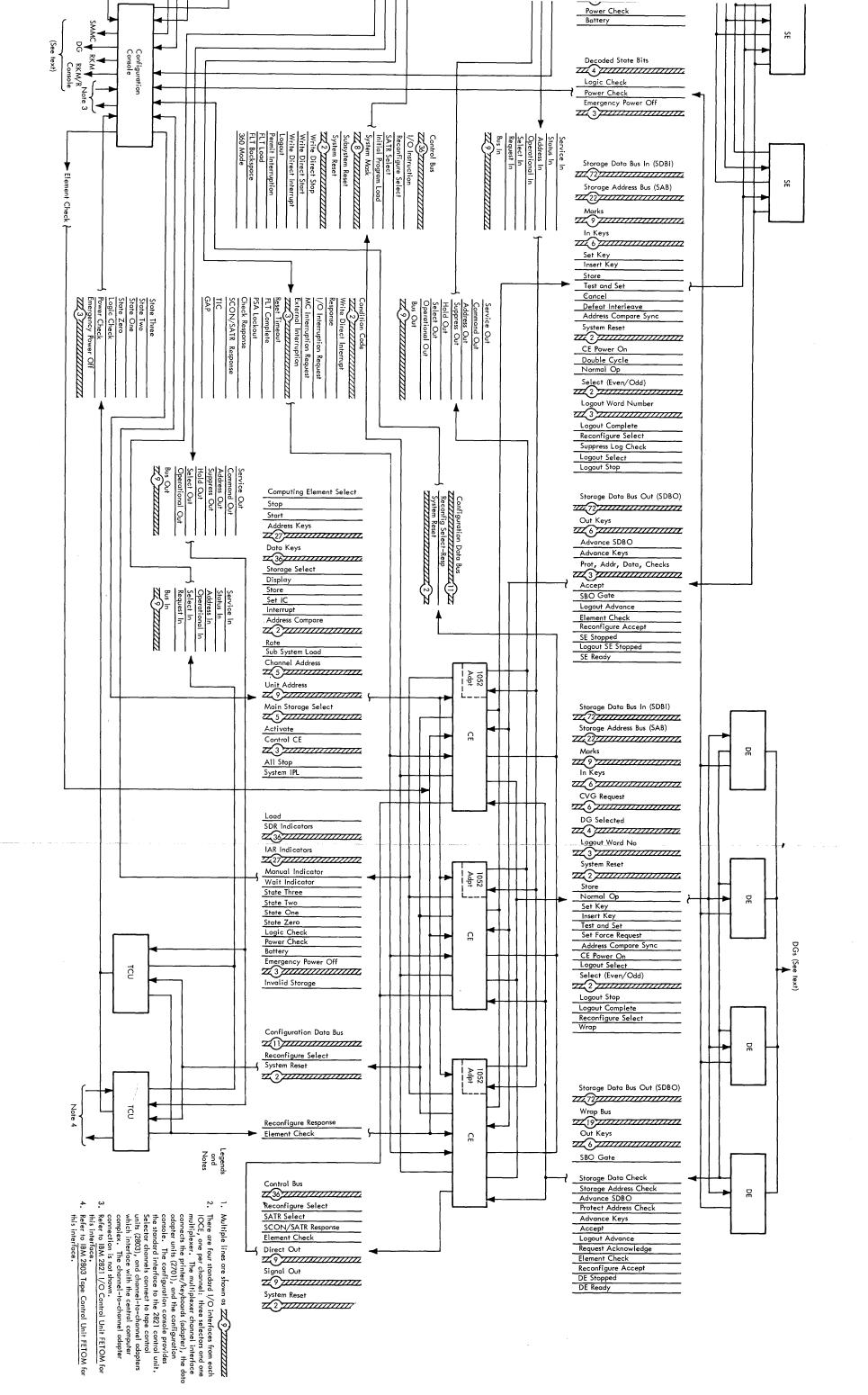

| CHAPTER 3 INTERFACE LINES                    | 3-1      |

| 1 0 0                                        | 3-1      |

| CE-CE Interfacing                            | 3-5      |

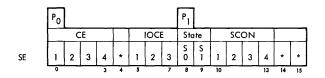

| CE-SE Interfacing                            | 3-7      |

| CE to SE Interface                           | 3-7      |

| SE to CE Interface                           | 3-9      |

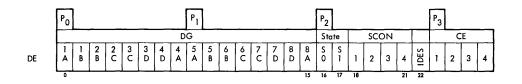

| CE-DE Interfacing                            | 3-11     |

|                                              | 3-11     |

| DE to CE Interface                           | 3-13     |

ς,

į

Ì.

ì

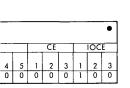

| CE-IOCE Interfacing                       | . 3-15                                                                  |

|-------------------------------------------|-------------------------------------------------------------------------|

| CE to IOCE Interface                      | . 3-16                                                                  |

| IOCE to CE Interface                      |                                                                         |

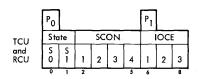

| CE-TCU Interfacing                        |                                                                         |

|                                           |                                                                         |

| CE to TCU Interface                       | . 3-19                                                                  |

| TCU to CE Interface                       |                                                                         |

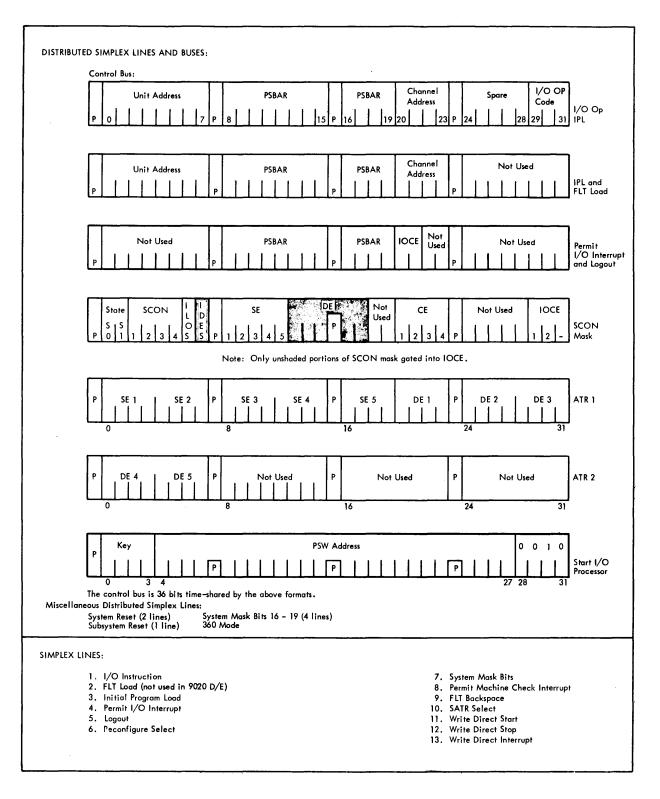

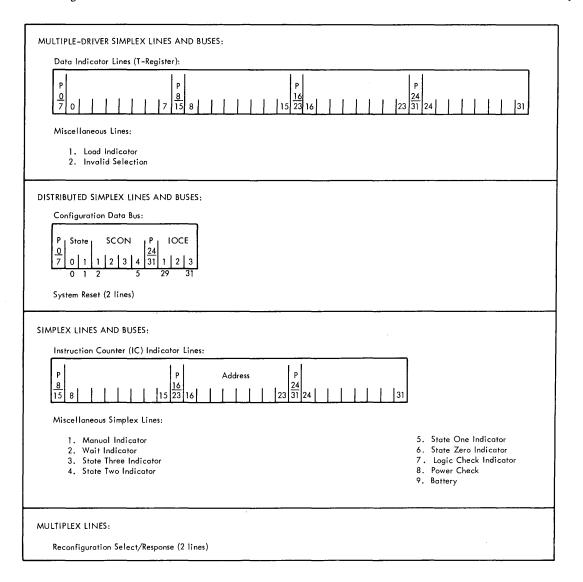

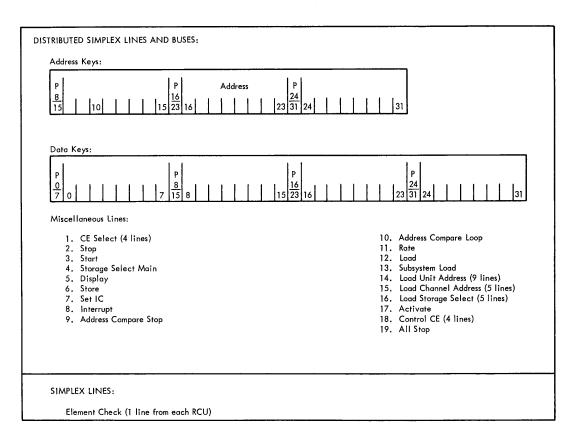

| CE-Configuration Console (CC) Interfacing | . 3-20                                                                  |

| CE to CC Interface                        | . 3-20                                                                  |

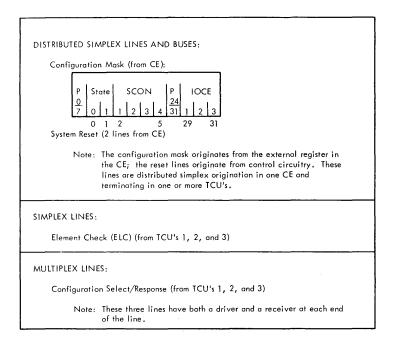

| CC to CE Interface                        | 3-22                                                                    |

| I/O Control Element Interfacing           |                                                                         |

|                                           |                                                                         |

| IOCE-CE Interfacing                       |                                                                         |

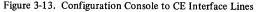

| IOCE-SE Interfacing                       |                                                                         |

| IOCE to SE Interface                      | . 3-24                                                                  |

| SE to IOCE Interface                      | . 3-26                                                                  |

| IOCE-Channel Interfacing                  | . 3-27                                                                  |

| IOCE-Configuration Console Interfacing    |                                                                         |

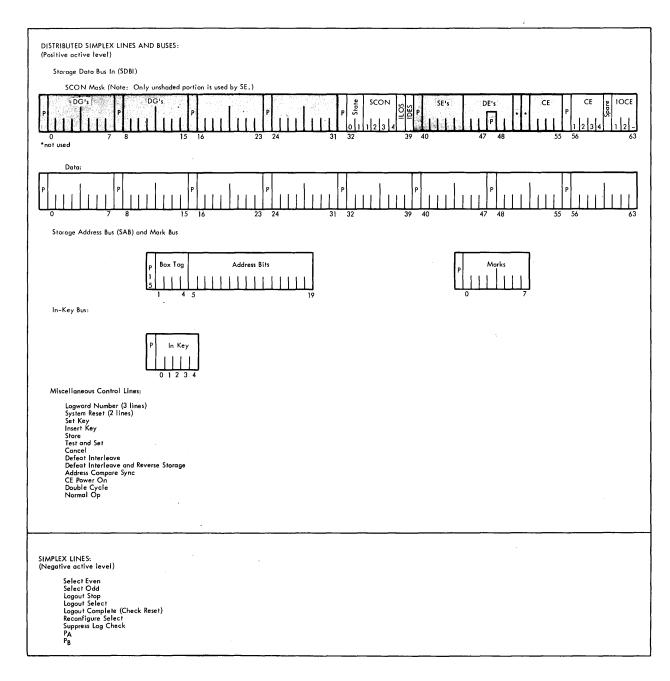

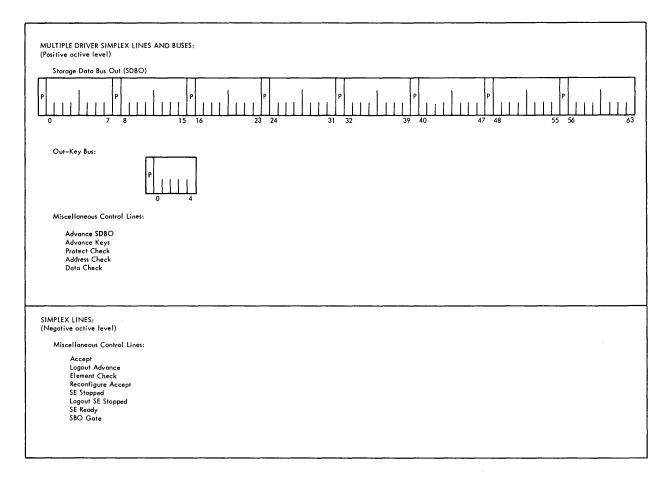

| SE Interfacing                            |                                                                         |

|                                           |                                                                         |

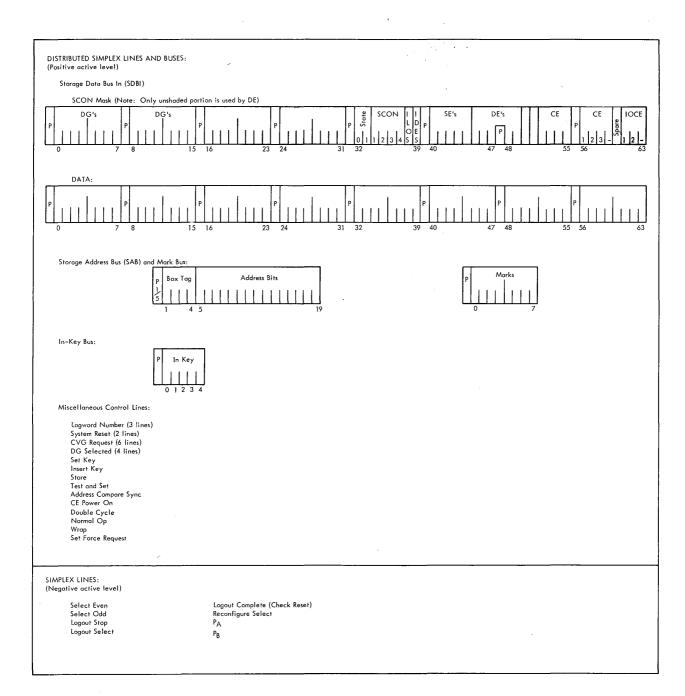

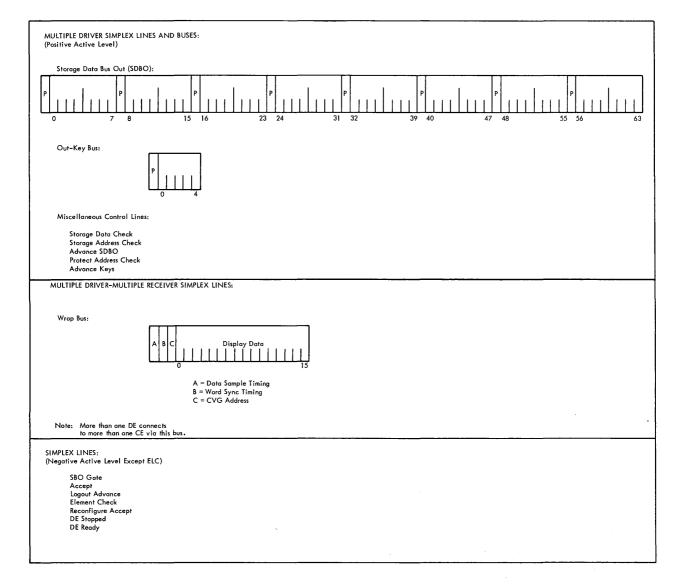

| DE Interfacing                            |                                                                         |

| DE-DG Interface                           |                                                                         |

| DE-CC Interface                           | . 3-30                                                                  |

| TCU Interfacing                           | 3-30                                                                    |

| DAU Interfacing                           |                                                                         |

| DAU-IOCE Interface                        | 2 2 1                                                                   |

|                                           |                                                                         |

| DAU-CC Interface                          |                                                                         |

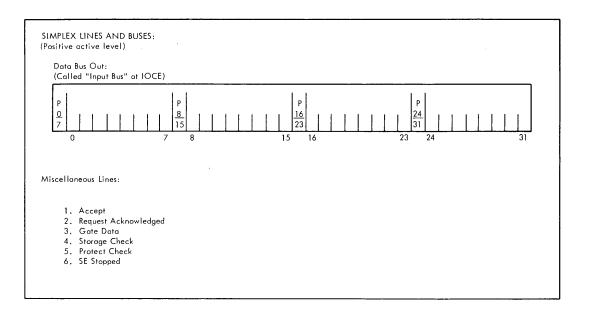

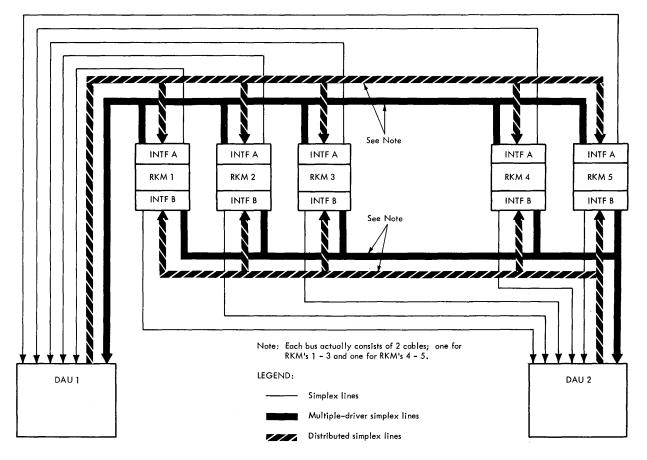

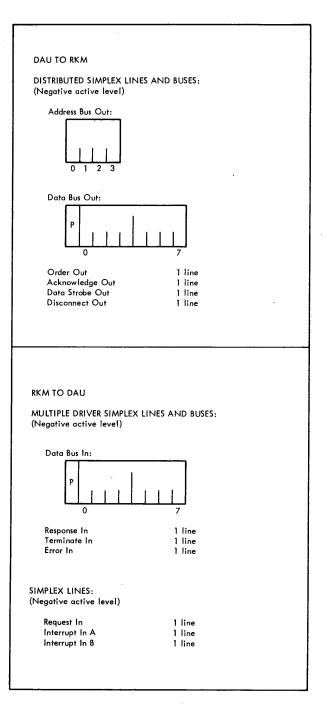

| DAU-RKM Interface                         |                                                                         |

| DAU-to-RKM Interface Lines                |                                                                         |

| RKM-to-DAU Interface Lines                | 3-33                                                                    |

| Configuration Console Interfacing         |                                                                         |

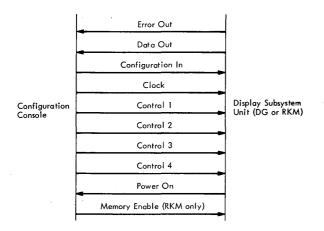

| DG and RKM Configuration Interface        | 226                                                                     |

|                                           | 2.20                                                                    |

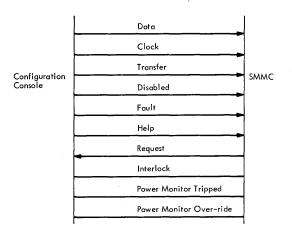

| CC-SMMC Interface                         |                                                                         |

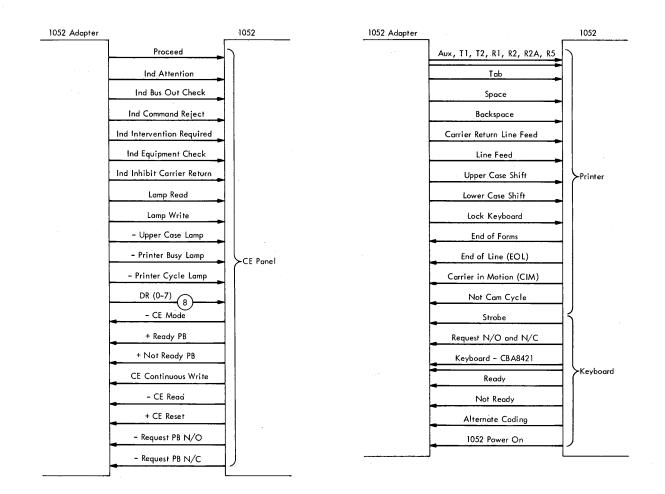

| 1052 Adapter - 1052 Interface             |                                                                         |

| Standard I/O Interface Summary            | 3-38                                                                    |

| Buses                                     | 3-38                                                                    |

| Bus Out                                   | 3-38                                                                    |

| Bus In                                    |                                                                         |

| Tag Lines                                 |                                                                         |

|                                           | 2 40                                                                    |

| Overall Interfacing                       | . 3-40                                                                  |

|                                           |                                                                         |

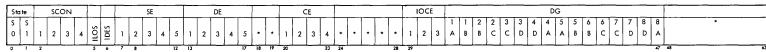

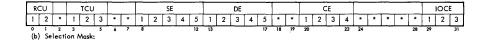

| CHAPTER 4 CONFIGURATION CONTROL           |                                                                         |

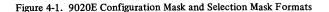

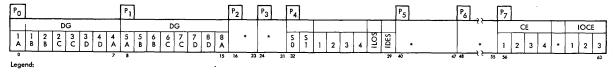

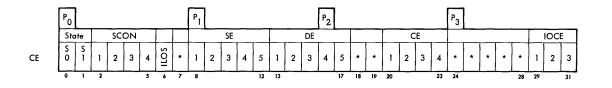

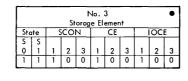

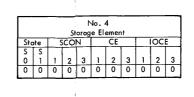

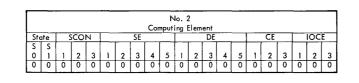

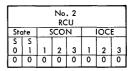

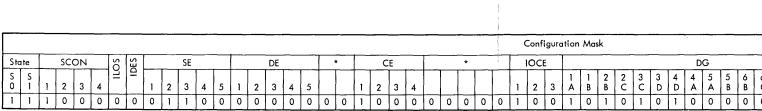

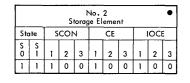

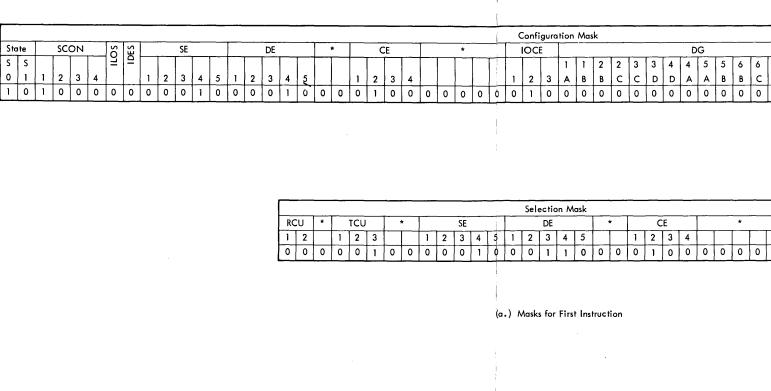

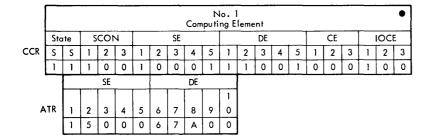

| Set Configuration Instruction (SCON)      | 4-2                                                                     |

| Configuration Mask                        | 4-2                                                                     |

| Selection Mask                            |                                                                         |

| Configuration Control Desister (CCD)      | 4-2                                                                     |

| Configuration Control Register (CCR)      | 4-5                                                                     |

| System Element States                     |                                                                         |

| State Three                               |                                                                         |

| State Two                                 | 4-6                                                                     |

| State One                                 | 4-6                                                                     |

| State Zero                                | 4-6                                                                     |

|                                           |                                                                         |

| CCR SCON Field                            | 4-7                                                                     |

| CCR SCON Field                            | 4-7                                                                     |

| CCR ILOS Field in CE and IOCE             | 4-8                                                                     |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8                                                              |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8                                                       |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8                                                              |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8                                                       |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-8                                         |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-8<br>4-8<br>4-9                           |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9                           |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9                    |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9                           |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-9                    |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-9                    |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-10<br>. 5-1          |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-10<br>. 5-1<br>. 5-3 |

| CCR ILOS Field in CE and IOCE             | 4-8<br>4-8<br>4-8<br>4-8<br>4-9<br>4-9<br>4-9<br>4-10<br>. 5-1<br>. 5-3 |

9020 E Introduction (7/70) v

| CE Accesses                                        |          |     | 5-4                 |

|----------------------------------------------------|----------|-----|---------------------|

| IOCE Accesses                                      |          |     | 5-4                 |

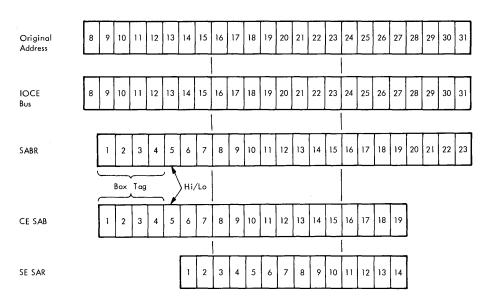

| SE Addressing Scheme                               |          |     | 5-4                 |

| Storage Interleaving                               |          | •   | 5-5                 |

| Addressing of Display Elements                     |          |     |                     |

| Storage Address Translation                        |          |     | 5-11                |

| Logical versus Physical Addresses                  |          |     | 5-11                |

| Normal Data Accesses                               |          |     |                     |

| PSA Accesses                                       |          |     |                     |

| Address Translation Register (ATR)                 |          |     |                     |

| Set Address Translator Instruction (SATR)          |          |     |                     |

| Insert Address Translator Instruction (IATR)       |          |     |                     |

| Address Translation Example No. 1                  |          | ·   | 5-16                |

| Address Translation Example No. 2                  | • •      | ·   | 5-16                |

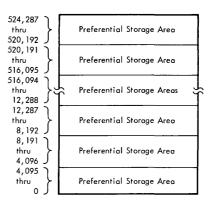

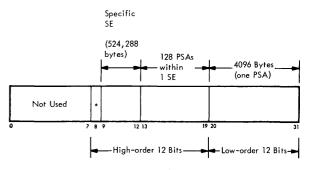

| Preferential Storage Areas (PSAs)                  | • •      | ·   | 5-23                |

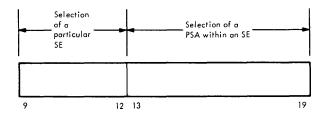

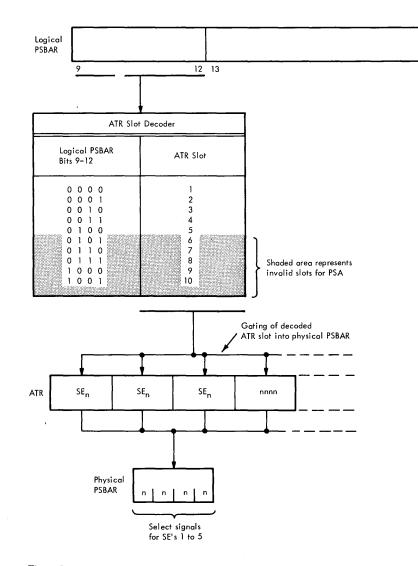

| Preferential Storage Base Address Register (PSBAR) | •        | ·   | 5-24                |

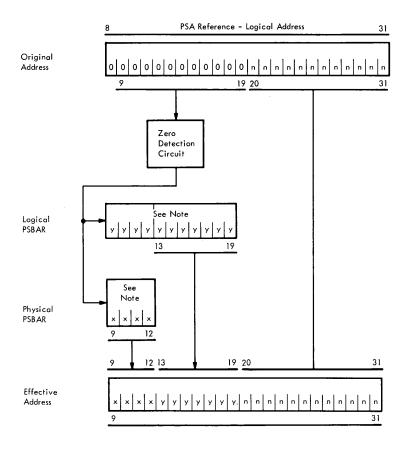

| Logical PSBAR                                      | • •      | ·   | 5-24                |

| Physical PSBAR                                     | •••      | ·   | 5-24                |

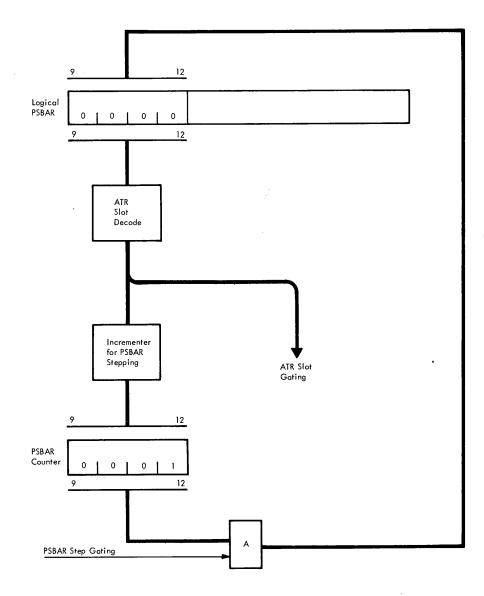

| PSBAR Counter                                      |          |     |                     |

| Load PSBA Instruction (LPSB)                       | • •      | ·   | 5-27                |

| Store PSBA Instruction (SPSB)                      | •••      | ·   | 5-28                |

| Operational Characteristics of PSBAR               |          |     |                     |

| PSA Example No. 1                                  |          |     |                     |

| PSA Example No. 2                                  |          |     |                     |

| IOCE PSBAR                                         | • •      | •   | 2-31                |

| CHAPTER 6 MULTISYSTEM OPERATION                    |          |     | 6-1                 |

|                                                    |          |     |                     |

| Direct Control                                     | • •      | •   | 6-2                 |

| Date Communication Command                         | • •      | •   | 6-2                 |

| Data Communication Command                         | • •      | •   | 6-2                 |

| CE Logout Command                                  | • •      | •   | 6-2                 |

| IOCE Logout Command                                | •••      | •   | 6-3                 |

| CE External Stop Command                           |          |     | 6-3                 |

| IOCE-Processor Stop Command                        |          |     | 6-3                 |

| IOCE-Processor Start Command                       |          |     |                     |

| IOCE-Processor Interrupt Command                   |          |     |                     |

| Read Direct Instruction (RDD)                      |          |     |                     |

| IOCE-Processor Write Direct Instruction (WRD)      |          |     |                     |

| Direct Control Example                             |          |     | 6-4                 |

| Data Communication                                 |          |     | 6-4                 |

| CE External Start                                  |          |     | 6-4                 |

|                                                    |          |     | 6-4                 |

| IOCE Logout                                        |          | •   | 6-4                 |

| Interrupts                                         |          | ٠   | 6-6                 |

| Machine Check Interrupt                            |          |     |                     |

| CE Machine Check Interrupt                         |          |     |                     |

| IOCE Machine Check Interrupt                       |          |     |                     |

| Program Interrupt                                  | • •      | ·   | 6-7                 |

| Supervisor Call Interrupt                          | • •      | ·   | 6-9                 |

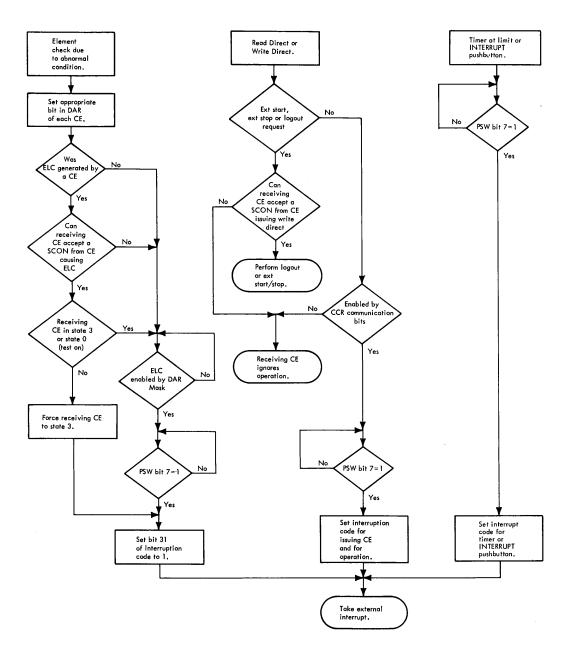

| External Interrupt                                 | • •      | ·   | 6-9                 |

| Timer Interrupt                                    |          |     |                     |

| Console Interrupt                                  | • •      | •   | 0-9                 |

| Direct Control Interrupts                          | • •      | •   | 6-10<br>6-10        |

| Abnormal Condition Signals                         |          |     |                     |

| Input/Output Interrupt                             | • •      | •   | 6-11                |

| IOCE-Processor PSW and Interrupt Action            | • •      | •   | 6-11                |

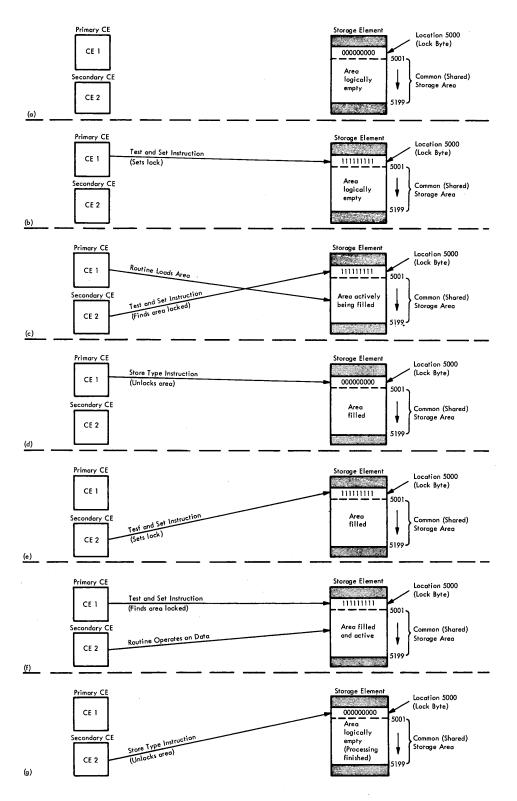

| Shared Storage                                     | • •      | ·   | 6-13                |

| Shared Storage                                     |          |     | 0 10                |

| Test and Set Instruction (TS)                      | •••      |     | 6-13                |

| Test and Set Instruction (TS)                      |          | •   | 6-13<br>6-13        |

| Test and Set Instruction (TS)                      | •••      | •   | 6-13                |

| Test and Set Instruction (TS)                      | •••      | •   | 6-13                |

| Test and Set Instruction (TS)                      | <br>     | •   | 6-13<br>6-13        |

| Test and Set Instruction (TS)                      | <br><br> | · · | 6-13<br>6-13<br>7-1 |

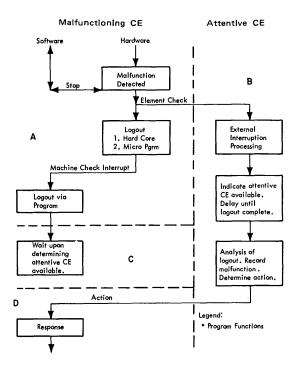

| Overall Operation                                                                                                                                                             | . 7-1                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitoring Facilities                                                                                                                                                         | . 7-2                                                                                                                                                                  |

| Interelement Signal Lines                                                                                                                                                     | . 7-2                                                                                                                                                                  |

| Logout                                                                                                                                                                        | . 7-2                                                                                                                                                                  |

| External Interruption                                                                                                                                                         |                                                                                                                                                                        |

| Normal Interruptions                                                                                                                                                          |                                                                                                                                                                        |

| Abnormal Interruptions                                                                                                                                                        | . 7-5                                                                                                                                                                  |

| Masking                                                                                                                                                                       | . 7-5                                                                                                                                                                  |

| PSW Interruption Code                                                                                                                                                         | . 7-5                                                                                                                                                                  |

| Diagnose Accessible Register (DAR)                                                                                                                                            | . 7-6                                                                                                                                                                  |

| Diagnose Accessible Register Mask (DARM)                                                                                                                                      | . 7-6                                                                                                                                                                  |

| System Monitoring of Abnormal Conditions                                                                                                                                      | . 7-7                                                                                                                                                                  |

| Power Supply Abnormal Conditions                                                                                                                                              |                                                                                                                                                                        |

| Marginal Temperature Condition (Out of Tolerance                                                                                                                              |                                                                                                                                                                        |

| Check or OTC)                                                                                                                                                                 | . 7-7                                                                                                                                                                  |

| Check or OTC)                                                                                                                                                                 | . 7-8                                                                                                                                                                  |

| CCR Parity Check                                                                                                                                                              | 7-8                                                                                                                                                                    |

| Checkstop                                                                                                                                                                     |                                                                                                                                                                        |

|                                                                                                                                                                               |                                                                                                                                                                        |

|                                                                                                                                                                               | • 1-9                                                                                                                                                                  |

| CHAPTER 8 ELEMENT MALFUNCTION HANDLING .                                                                                                                                      | 0.1                                                                                                                                                                    |

|                                                                                                                                                                               |                                                                                                                                                                        |

| Error Recording                                                                                                                                                               |                                                                                                                                                                        |

| Logout                                                                                                                                                                        |                                                                                                                                                                        |

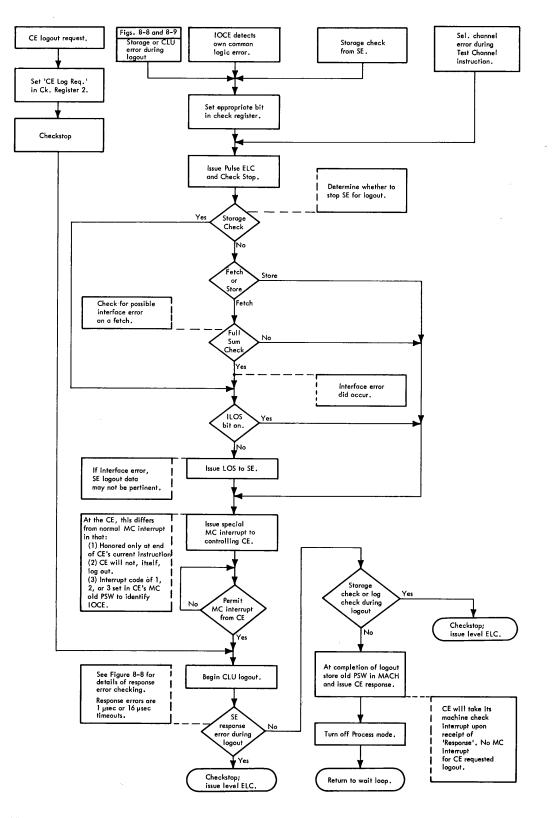

| CE Logout                                                                                                                                                                     |                                                                                                                                                                        |

| IOCE Logout                                                                                                                                                                   | . 8-3                                                                                                                                                                  |

| SE Logout                                                                                                                                                                     |                                                                                                                                                                        |

| DE Logout                                                                                                                                                                     |                                                                                                                                                                        |

| Split Logout                                                                                                                                                                  |                                                                                                                                                                        |

| Sense Command                                                                                                                                                                 | . 8-5                                                                                                                                                                  |

| Malfunction Handling                                                                                                                                                          | . 8-5                                                                                                                                                                  |

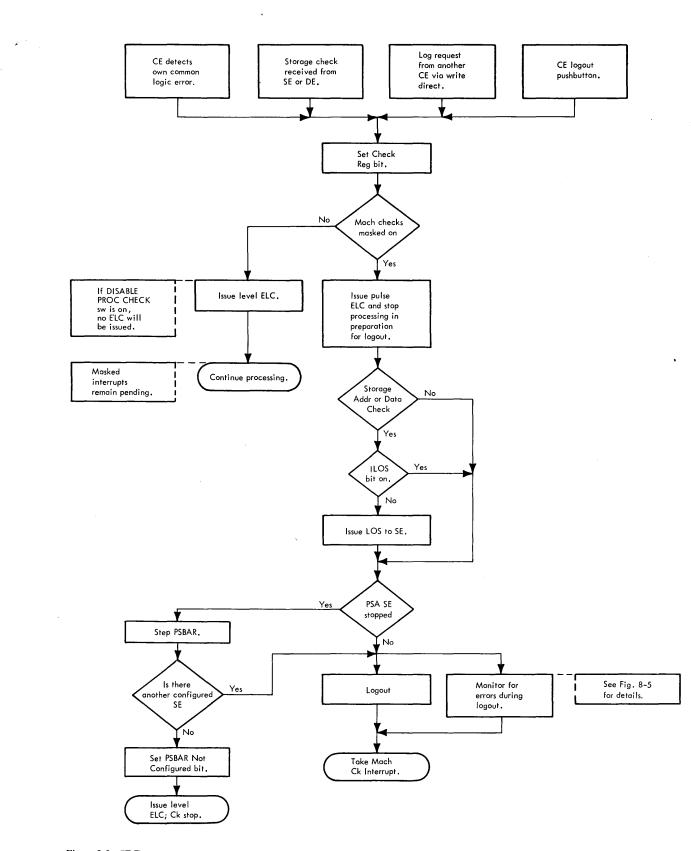

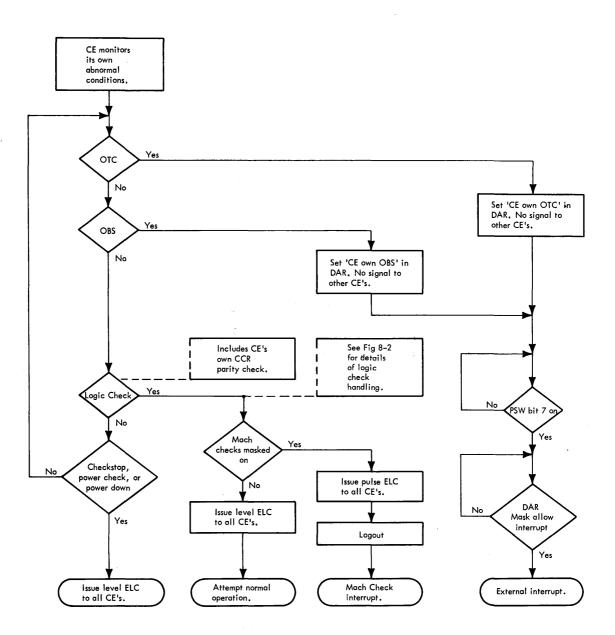

| CE Error Handling                                                                                                                                                             | . 8-6                                                                                                                                                                  |

| Logic Checks                                                                                                                                                                  |                                                                                                                                                                        |

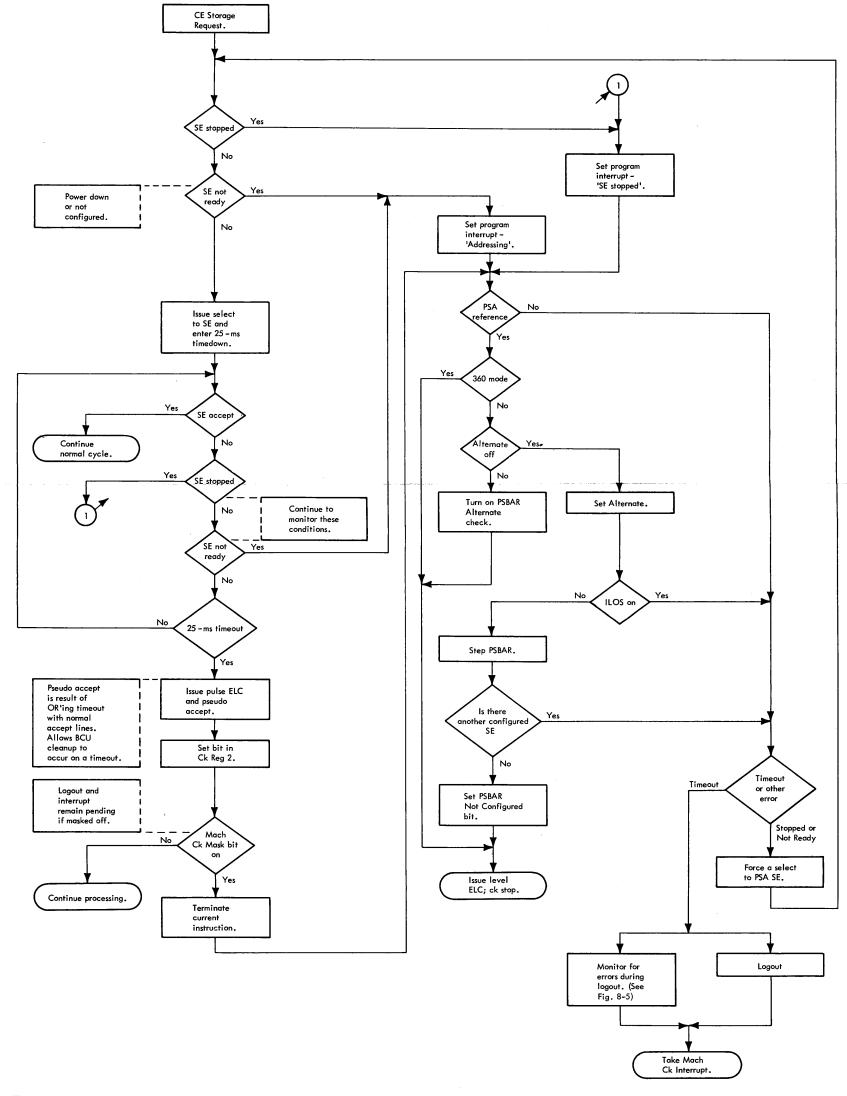

| CE Handling of SE Access Response Errors                                                                                                                                      |                                                                                                                                                                        |

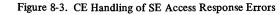

| CE Handling of DE Access Response Errors                                                                                                                                      |                                                                                                                                                                        |

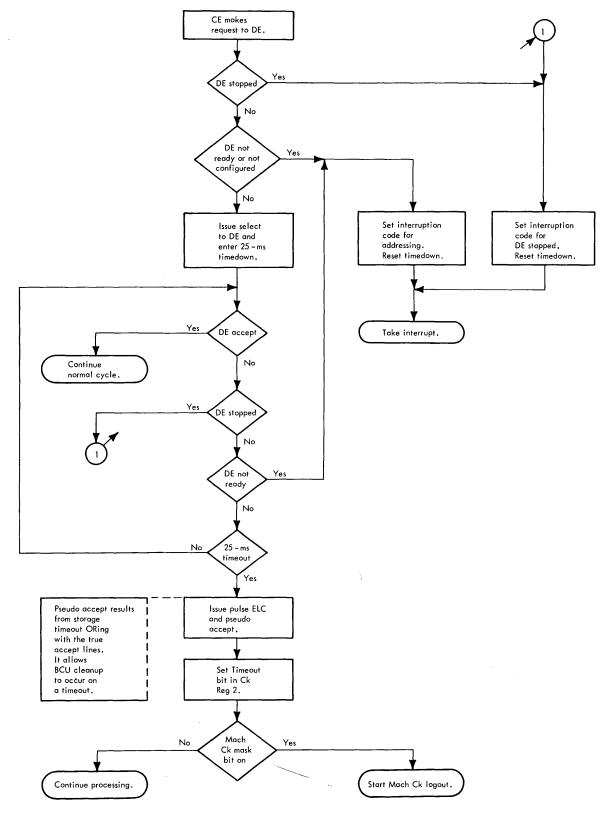

| CE Error Monitoring during Logout                                                                                                                                             |                                                                                                                                                                        |

| CE Handling of Internal Abnormal Conditions                                                                                                                                   |                                                                                                                                                                        |

| IOCE Error Handling                                                                                                                                                           | . 8-11                                                                                                                                                                 |

| IOCE Handling of SLU Errors                                                                                                                                                   | . 8-15                                                                                                                                                                 |

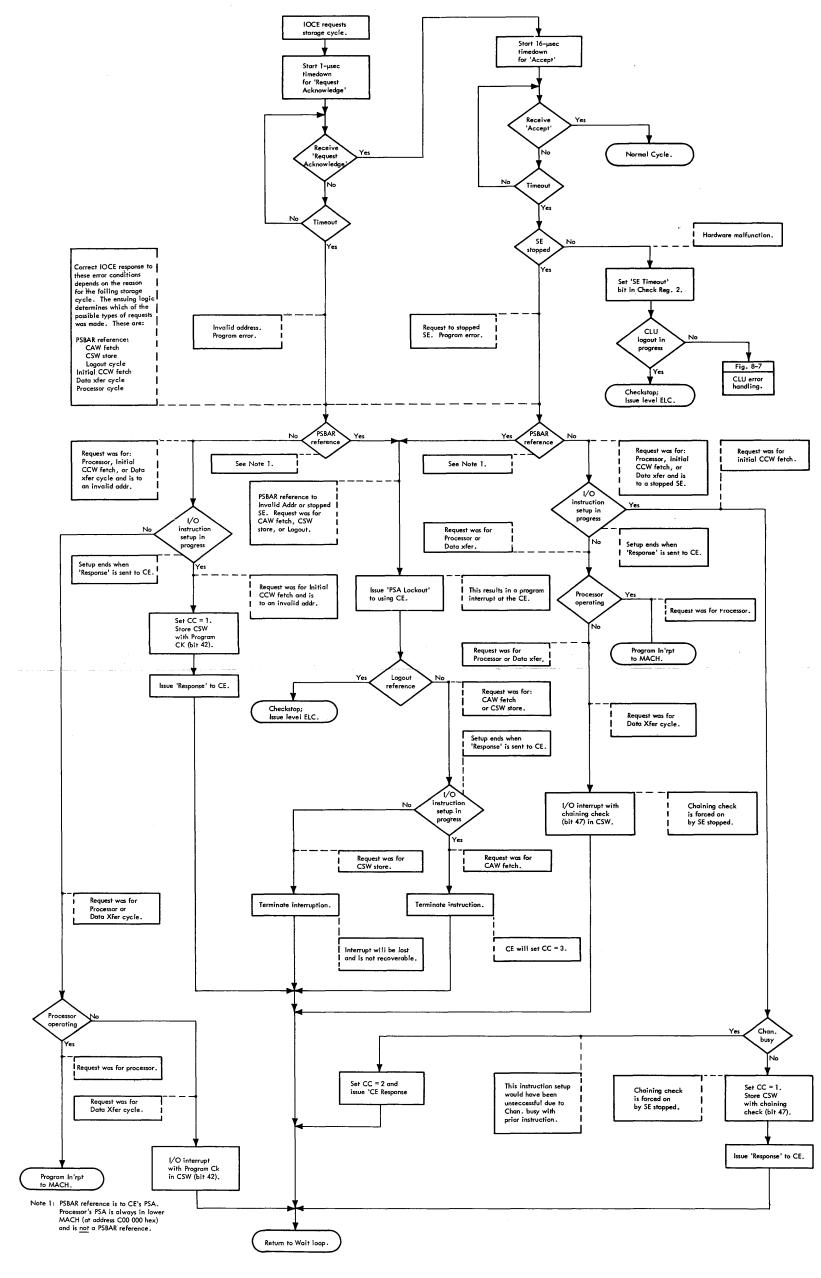

| IOCE Handling of SE Access Response Errors                                                                                                                                    | . 8-16                                                                                                                                                                 |

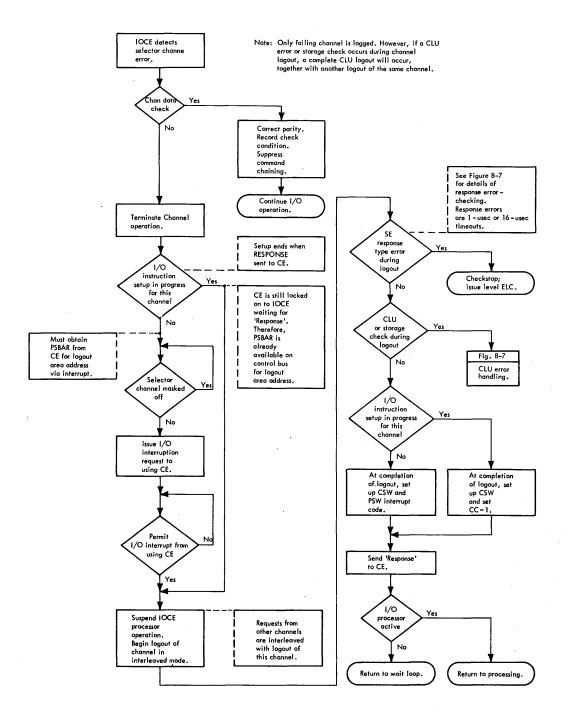

| IOCE Handling of Selector Channel Errors                                                                                                                                      | . 8-18                                                                                                                                                                 |

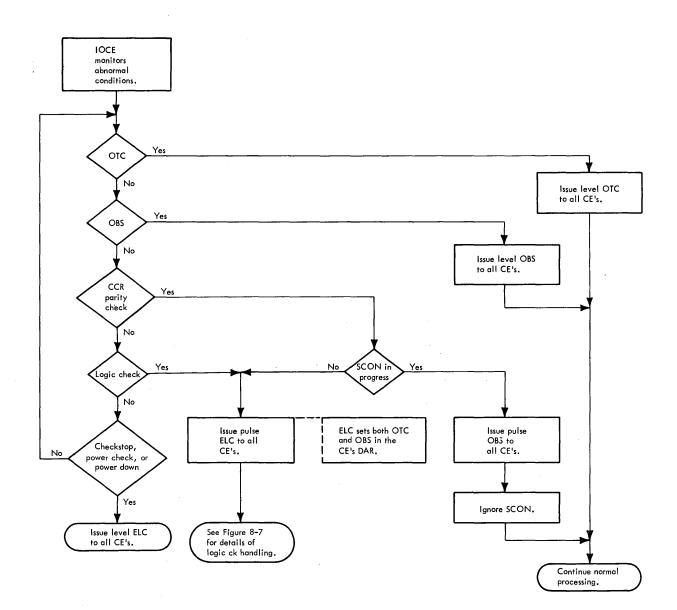

| IOCE Handling of Abnormal Conditios                                                                                                                                           |                                                                                                                                                                        |

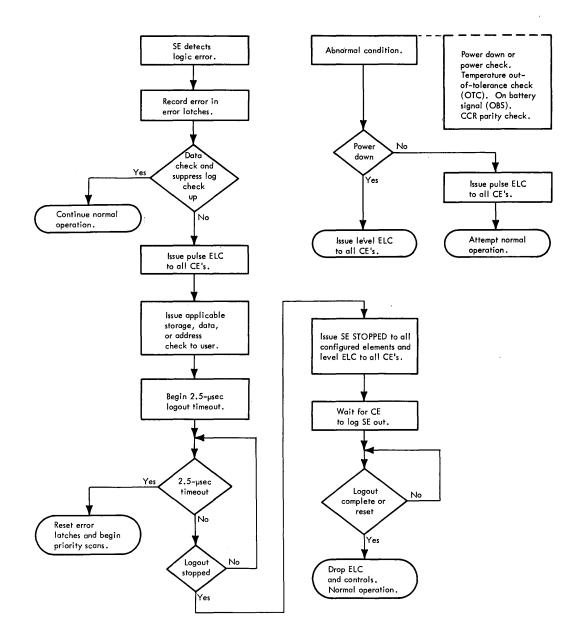

| SE Error Handling                                                                                                                                                             | . 8-21                                                                                                                                                                 |

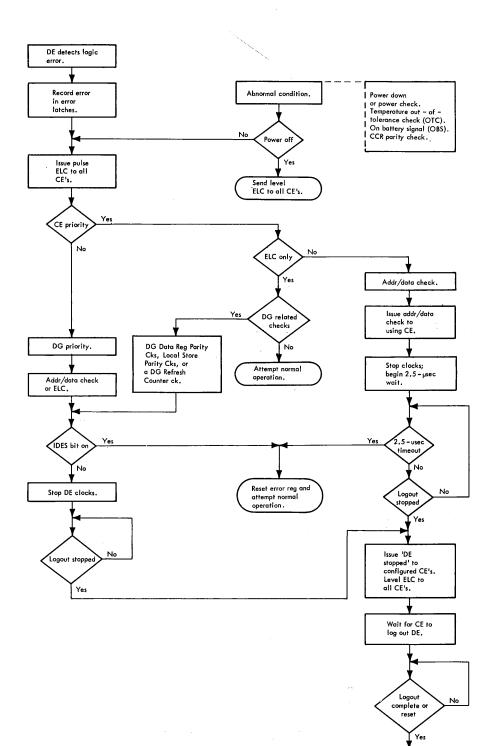

| DE Error Handling                                                                                                                                                             | . 8-25                                                                                                                                                                 |

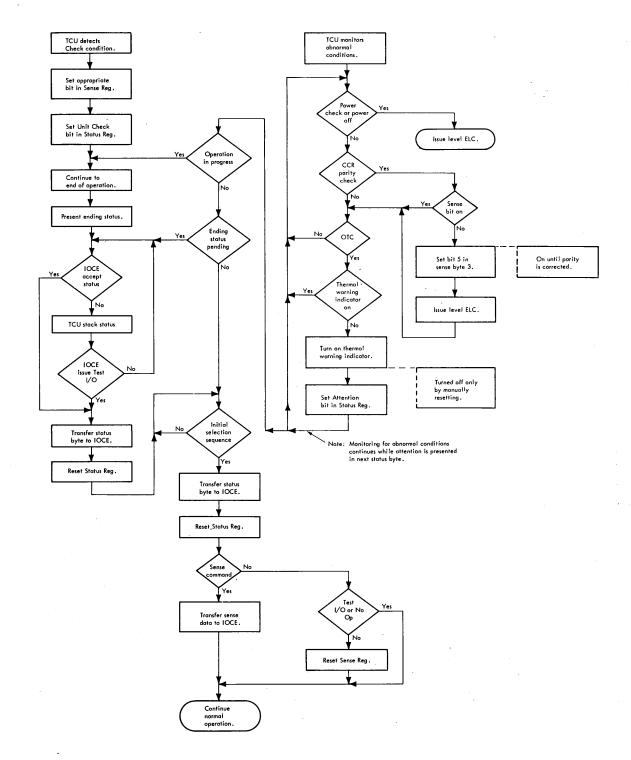

| TCU Error Handling                                                                                                                                                            |                                                                                                                                                                        |

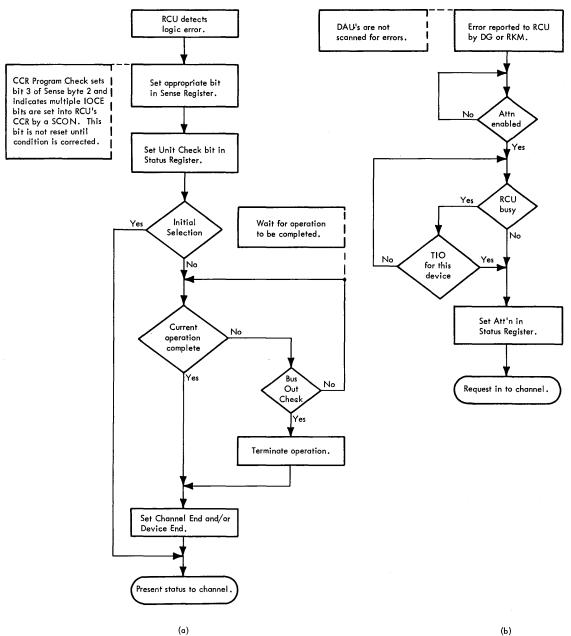

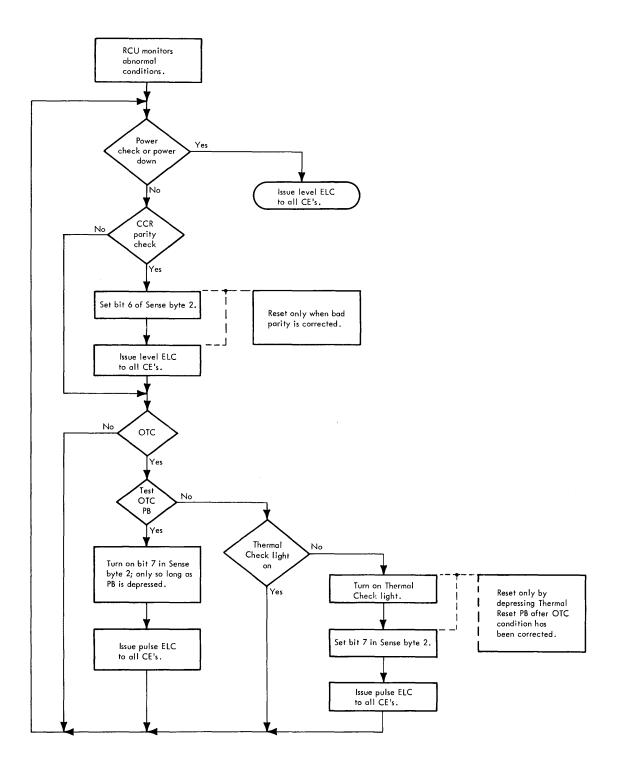

| RCU Error Handling                                                                                                                                                            |                                                                                                                                                                        |

|                                                                                                                                                                               |                                                                                                                                                                        |

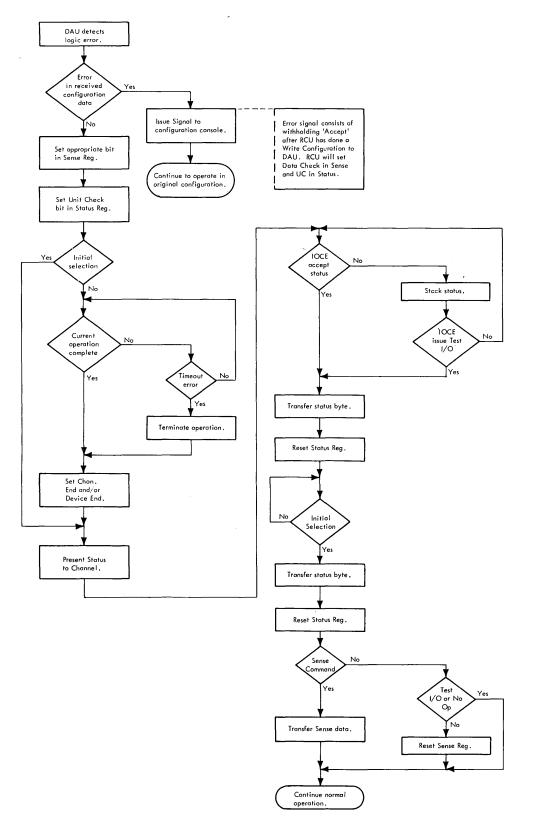

| DAU Error Handling                                                                                                                                                            | . 8-30                                                                                                                                                                 |

| DAU Error Handling                                                                                                                                                            | . 8-30                                                                                                                                                                 |

|                                                                                                                                                                               |                                                                                                                                                                        |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1                                                                                                                                                                  |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1                                                                                                                                                         |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1                                                                                                                                                |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1                                                                                                                                       |

| CHAPTER 9 SYSTEM INITIALIZATION          Resets          System Reset          Subsystem Reset          Initial Program Load (IPL)                                            | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3                                                                                                                              |

| CHAPTER 9 SYSTEM INITIALIZATION          Resets          System Reset          Subsystem Reset          Initial Program Load (IPL)          System IPL                        | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3                                                                                                                     |

| CHAPTER 9 SYSTEM INITIALIZATION          Resets          System Reset          Subsystem Reset          Initial Program Load (IPL)          System IPL                        | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3                                                                                                            |

| CHAPTER 9 SYSTEM INITIALIZATION          Resets          System Reset          Subsystem Reset          Initial Program Load (IPL)          System IPL          Subsystem IPL | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3                                                                                                                     |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3                                                                                                            |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3                                                                                                            |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3                                                                                                            |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3                                                                                          |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | . 9-1<br>. 9-1<br>. 9-1<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3<br>. 9-3                                                                                          |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | <ul> <li>9-1</li> <li>9-1</li> <li>9-1</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>8-1</li> <li>B-1</li> </ul>                                        |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | <ul> <li>9-1</li> <li>9-1</li> <li>9-1</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>8-1</li> <li>B-1</li> </ul>                                        |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | <ul> <li>9-1</li> <li>9-1</li> <li>9-1</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>4-1</li> <li>B-1</li> <li>B-1</li> </ul>              |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | <ul> <li>9-1</li> <li>9-1</li> <li>9-1</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>8-1</li> <li>B-1</li> </ul>                                        |

| CHAPTER 9 SYSTEM INITIALIZATION                                                                                                                                               | <ul> <li>9-1</li> <li>9-1</li> <li>9-1</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>9-3</li> <li>A-1</li> <li>B-1</li> <li>B-1</li> <li>G-1</li> </ul> |

# ILLUSTRATIONS

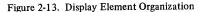

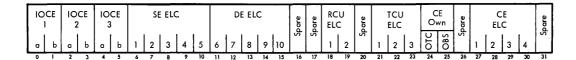

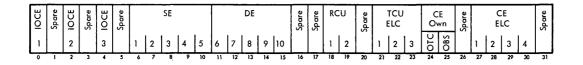

| Frontispiece | IBM 9020E Display Channel Processor           | 4-5          |

|--------------|-----------------------------------------------|--------------|

| 1-1          | Role of 9020E DCP in NAS En Route Stage       | 4-6<br>4-7   |

| 1-2          | A Complex 1-1<br>Function of DCP Elements 1-4 | 4-7          |

| 1-2<br>1-3   | Processing of Display Data 1-5                | 4-8          |

| 1-4          | Typical 9020E Display Channel Processor 1-7   | 4-9          |

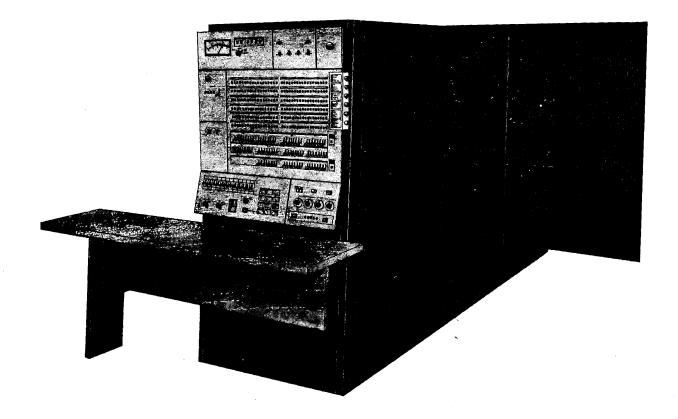

| 2-1          | IBM 7201-02 Computing Element (CE) 2-2        | .,           |

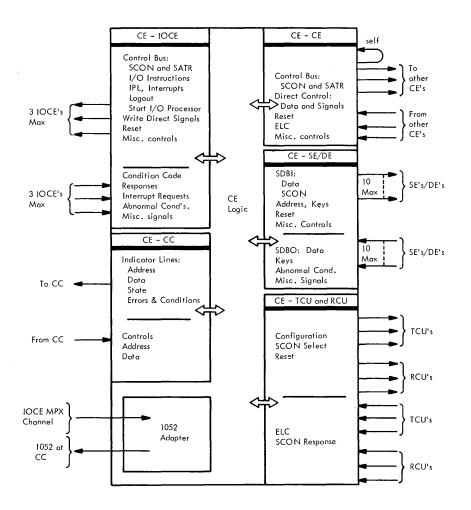

| 2-2          | Computing Element Interfacing 2-3             | 5-1          |

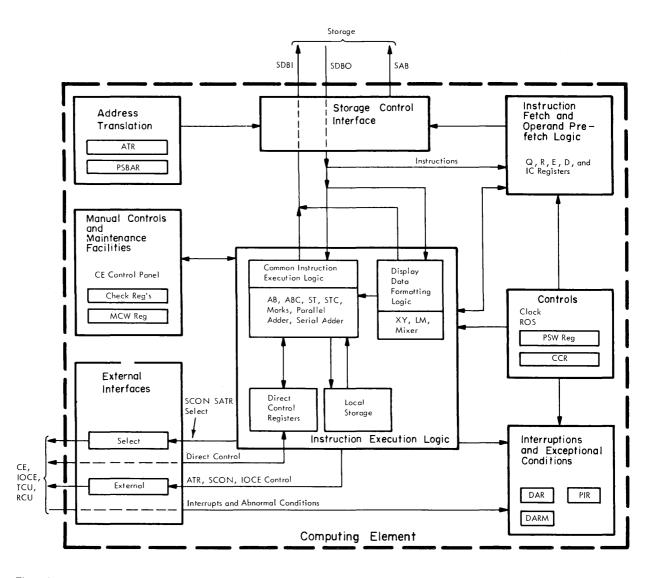

| 2-3          | Computing Element Internal Organization . 2-5 | 5-2          |

| 2-4          | IBM 7231-02 I/O Control Element (IOCE) . 2-7  | 5-3          |

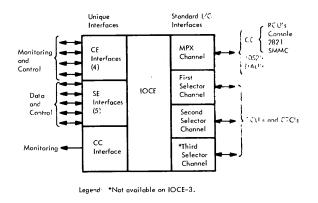

| 2-5          | IOCE Interfacing 2-8                          | 5-4          |

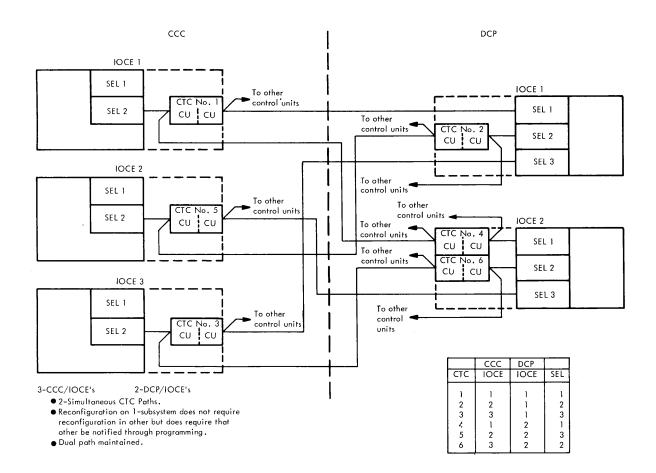

| 2-6          | Sample Channel-to-Channel Adapter Usage . 2-9 | 5-5          |

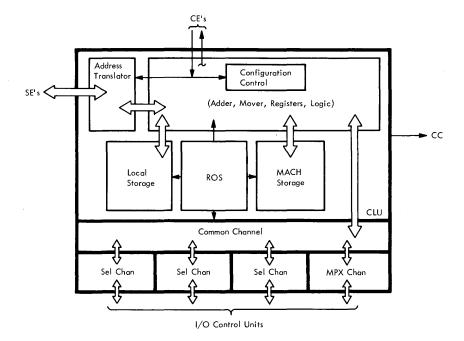

| 2-7          | IOCE Internal Organization 2-10               | 5-6          |

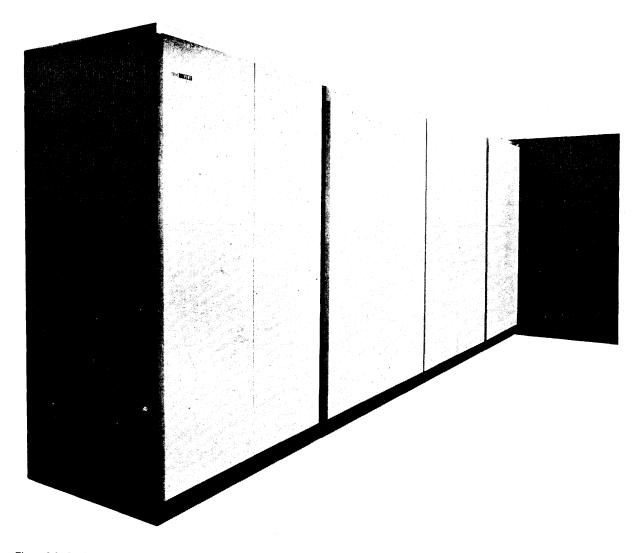

| 2-8          | IBM 7251-09 Storage Element (SE) 2-12         |              |

| 2-9          | SE Address Range (Bytes) 2-13                 | 5-7          |

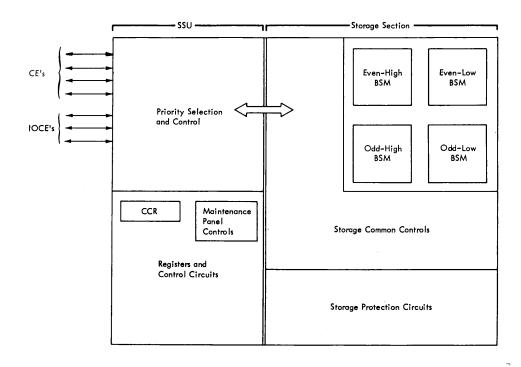

| 2-10         | Storage Element Organization 2-14             |              |

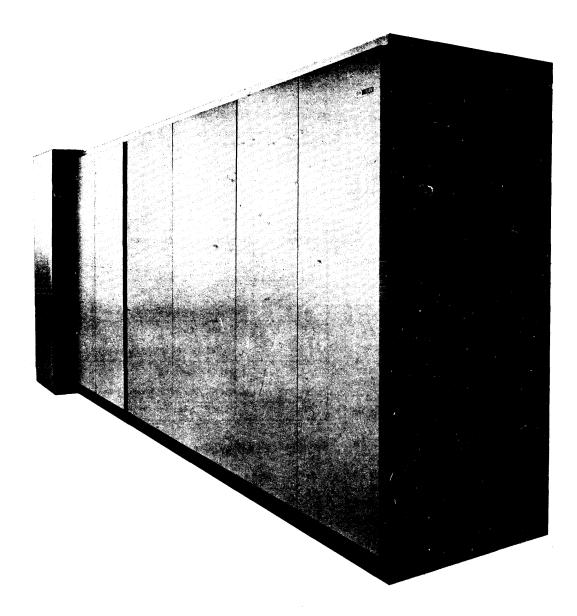

| 2-11         | IBM 7289-04 Display Element (DE) 2-15         | 5-8          |

| 2-12         | DE Address Ranges (Bytes) 2-16                |              |

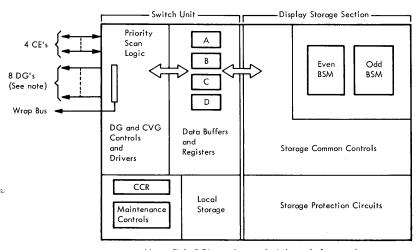

| 2-13         | Display Element Organization 2-17             | 5-9          |

| 2-14         | IBM 7265-03 Configuration Console (CC) . 2-18 | 5-10         |

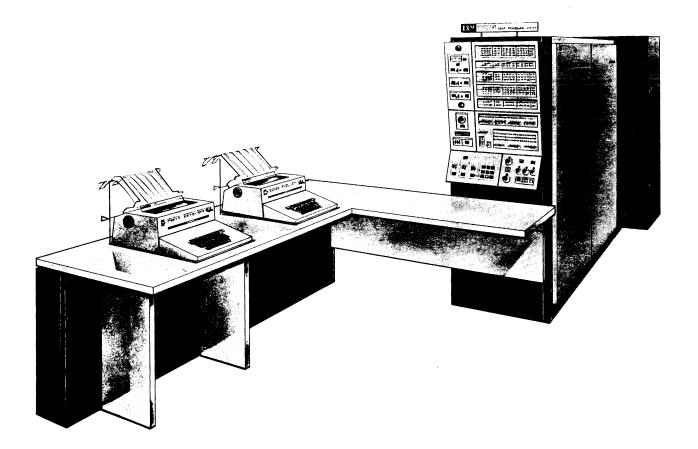

| 2-15         | Configuration Console Functions 2-19          |              |

| 2-16         | Configuration Console Internal                | 5-11         |

| 2.17         | Organization                                  | 5-12         |

| 2-17         | IBM 2701-01 Data Adapter Unit (DAU) 2-22      | 5-13         |

| 2-18<br>2-19 | DAU Internal Organization                     | 3-13         |

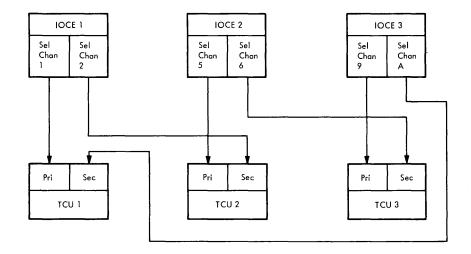

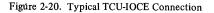

| 2-19         | Typical TCU-IOCE Connection 2-25              | 5-14         |

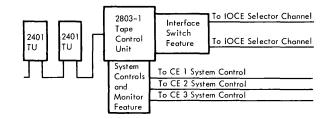

| 2-20         | TCU-I/O Device Connection                     | 5-14         |

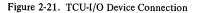

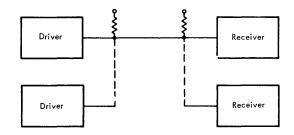

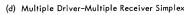

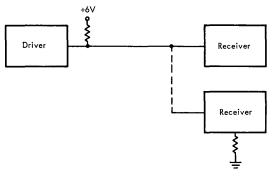

| 3-1          | Interface Receiver-Driver Combinations        | 5-16         |

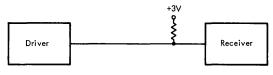

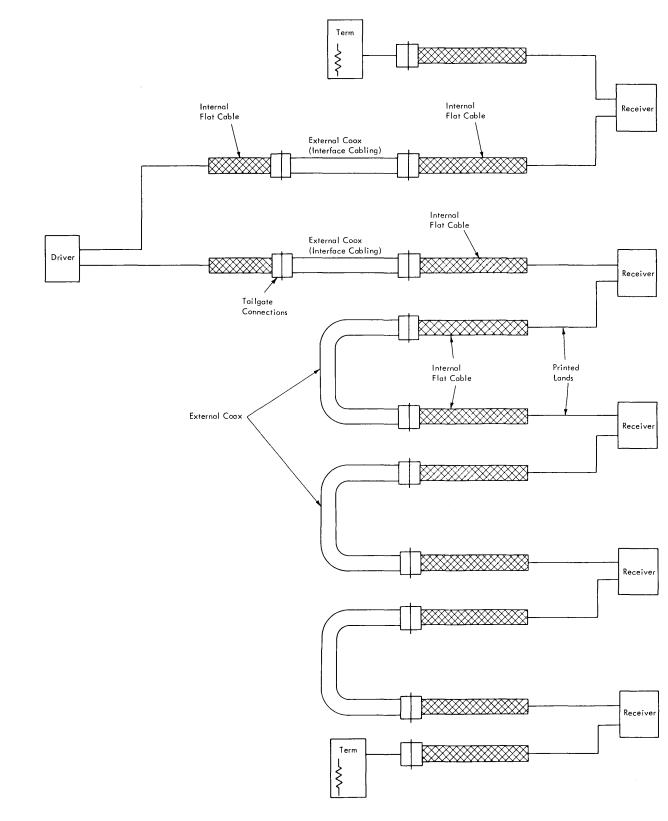

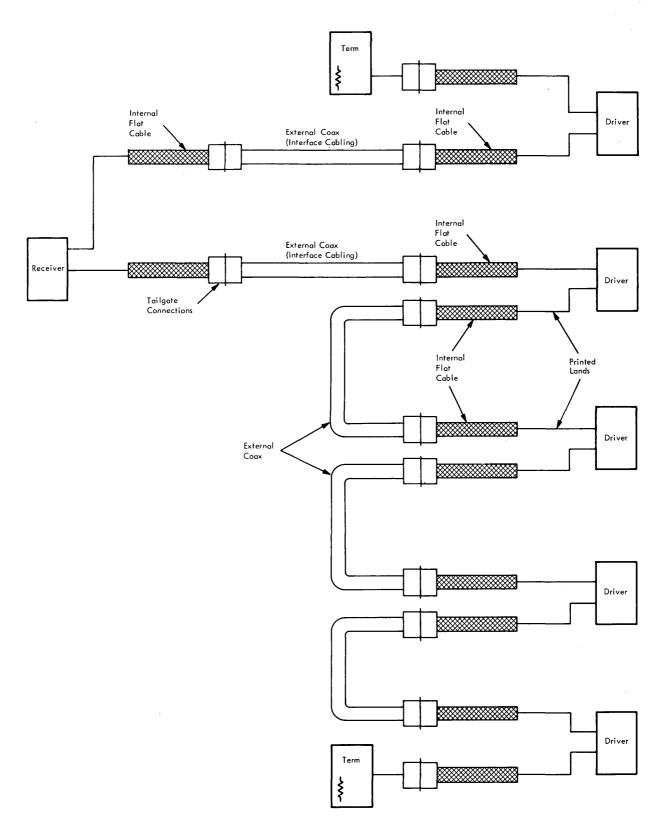

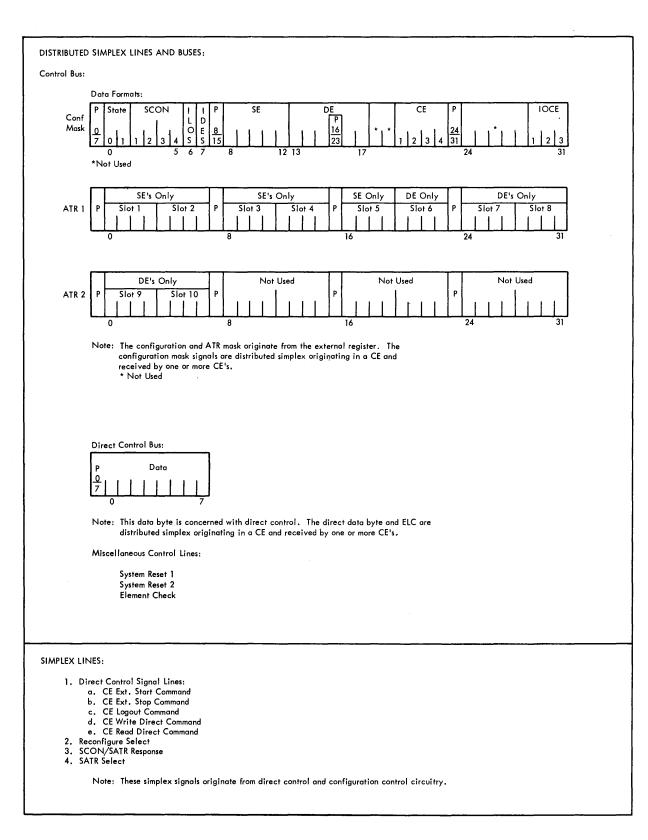

| 3-2          | Typical Distributed Simplex Interface         | 5-17         |

| 3-3          | Typical Multiple Driver Simplex Interface     | 5-18         |

| 3-4          | CE to CE Interface Lines                      | 5-19         |

| 3-5          | CE to SE Interface Lines                      | 5-20         |

| 3-6          | SE to CE Interface Lines                      | 5-21         |

| 3-7          | CE to DE Interface Lines                      |              |

| 3-8          | DE to CE Interface Lines                      | 5-22         |

| 3-9          | CE to IOCE Interface Lines                    | 5-23         |

| 3-10         | IOCE to CE Interface Lines 3-18               | 5-24         |

| 3-11         | Interface Lines between CE and TCU 3-20       | 5-25         |

| 3-12         | CE to Configuration Console Interface         | 5-26         |

|              | Lines                                         | 6-1          |

| 3-13         | Configuration Console to CE Interface         |              |

|              | Lines                                         | 6-2          |

| 3-14         | IOCE to SE Interface Lines 3-25               | 6-3          |

| 3-15         | SE to IOCE Interface Lines                    | 6-4          |

| 3-16         | DAU Interfacing                               |              |

| 3-17         | DAU-RKM Interfacing                           | 6-5          |

| 3-18         | DAU-RKM Interface Lines                       | 6-6          |

| 3-19         | Configuration Console Interfacing,            | (7           |

| 3-20         | Overall View                                  | 6-7<br>6-8   |

| 5-20         | DG and RKM Configuration Interface            | 6-8<br>6-9   |

| 3-21         | Lines                                         | 0-9<br>7-1   |

| 3-22         | 1052 Adapter 1052 Interface 2 20              | 7-1          |

| 3-23         | 1052 Adapter - 1052 Interface                 | 1-2          |

| 3-23<br>4-1  | 9020E Overall Interfacing                     | 7-3          |

| T 1          | Mask Formats                                  | 7-3<br>7-4   |

| 4-2          | SDBI Configuration Data Format 4-3            | 7 <b>-</b> 5 |

| 4-3          | 9020E Configuration Control Register          | 7-6          |

|              | Formats                                       | -            |

| 4-4          | Summary of State Definitions 4-5              | 8-1          |

|              | -,                                            |              |

|              | -                                             |              |

ŝ

ţ

ì.

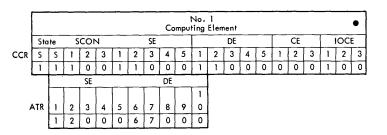

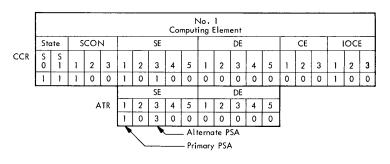

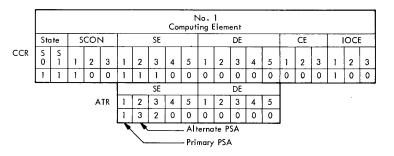

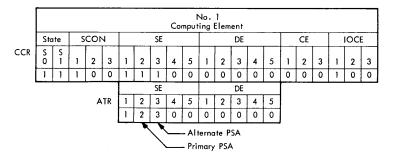

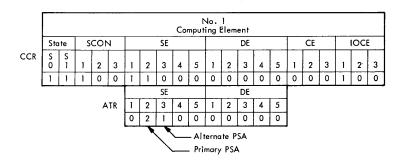

| CCR Field Examples                       | 4-7        |

|------------------------------------------|------------|

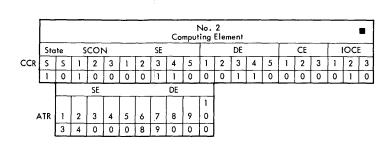

| Configuration Example No. 1              | 4-11       |

| SCON Instructions for Configuration      |            |

| Example No. 1                            | 4-13       |

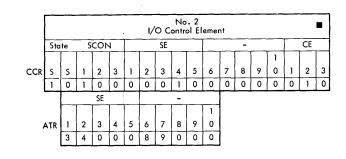

| Configuration Example No. 2              | 4-15       |

| SCON Instruction for Configuration       |            |

| Example No. 2                            | 4-17       |

| 9020E Storage Address Ranges             | 5-2        |

| Storage Addressing Formats               | 5-2        |

| Storage Addressing Formats               | 5-3        |

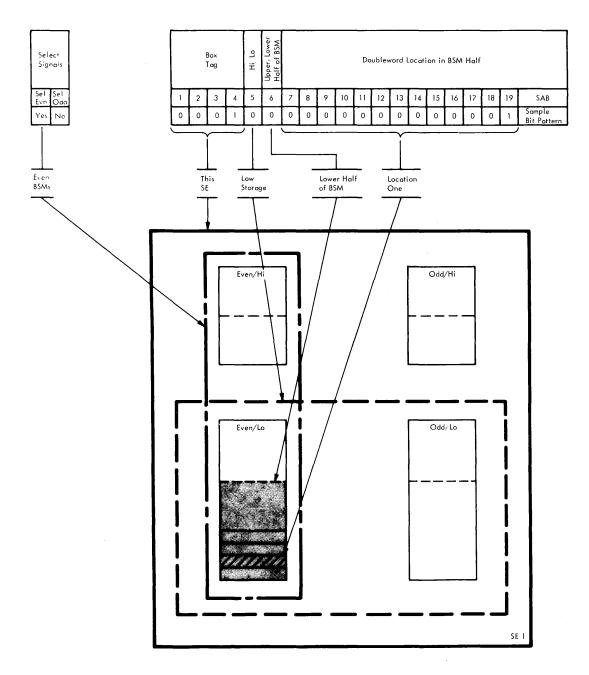

| Even and Odd Basic Storage Modules       | 3-3        |

| SE Doubleword Location Example           | 5-6        |

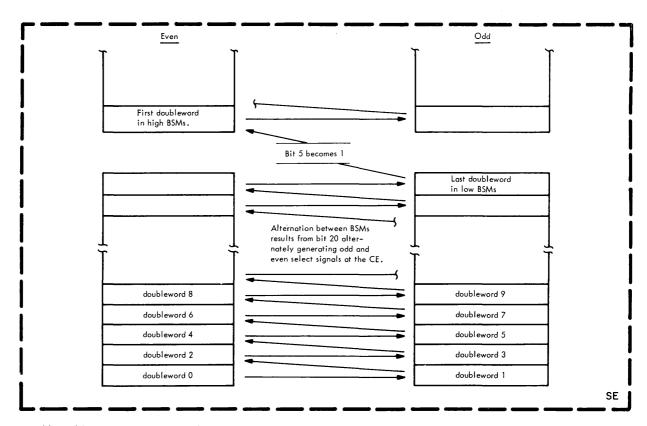

| Even and Odd Doublewords                 | 5-6        |

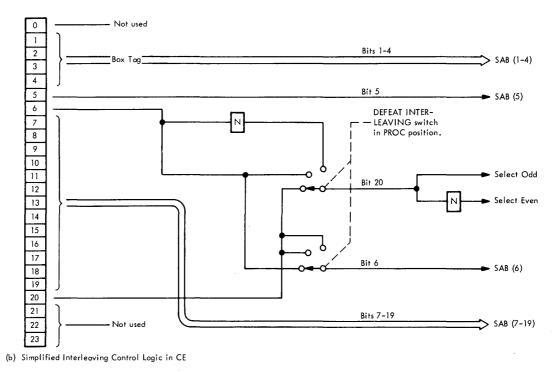

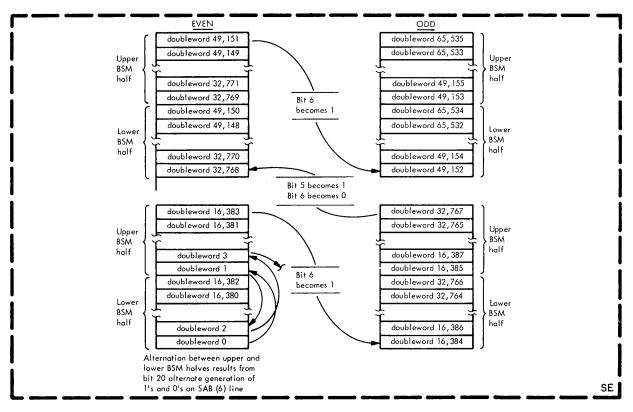

| Consecutive Doubleword Locations         |            |

| (Normal Interleaving)                    | 5-7        |

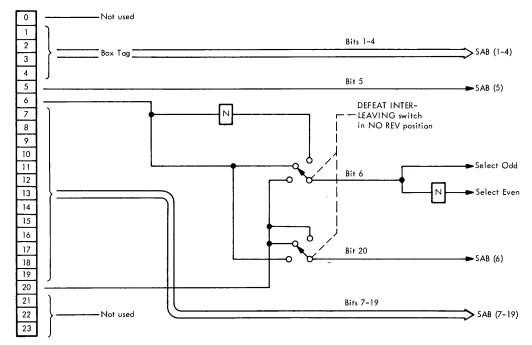

| Consecutive Doubleword Locations         |            |

| (Interleaving Defeated)                  | 5-8        |

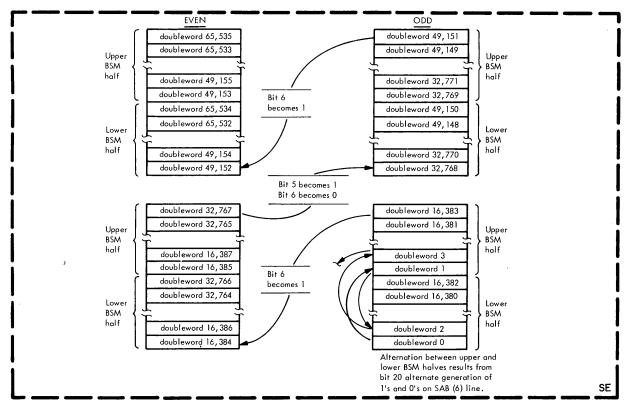

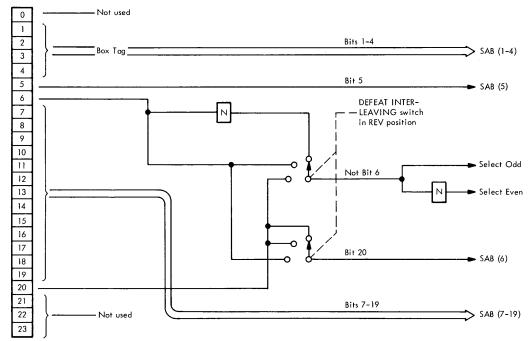

| Consecutive Doubleword Locations (Inter- |            |

| leaving Defeated and Storage Reversed) . | 5-10       |

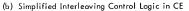

| Address Translation Simplified           | 5-12       |

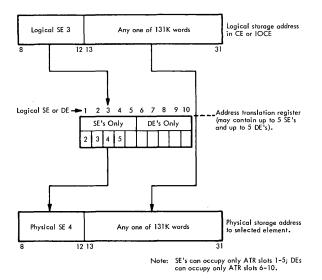

| Preferential Storage Address (PSA)       | 5-12       |

|                                          | E 12       |

| Formation                                | 5-13       |

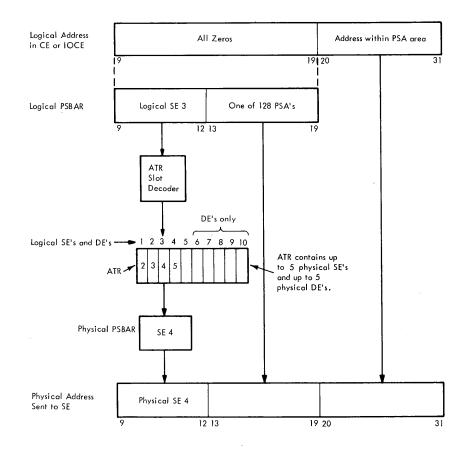

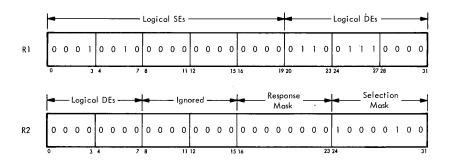

| Address Translation Register             | 5-14       |

| Register Formats as Specified by R1      |            |

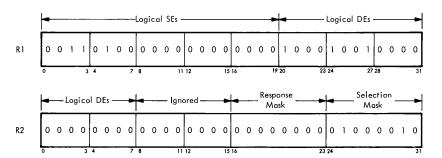

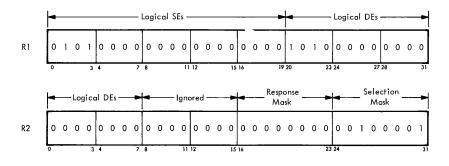

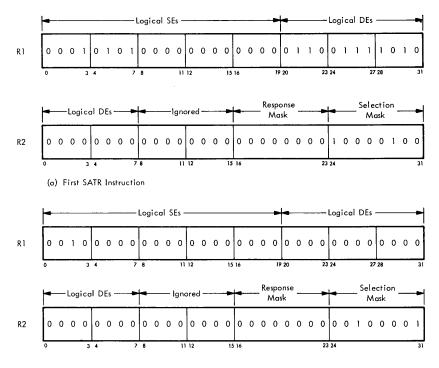

| and R2 of the SATR Instruction           | 5-14       |

| Selection and Response Mask Formats for  |            |

| the SATR Instruction                     | 5-14       |

| Address Translation Example No. 1        | 5-17       |

| SATR Formats for Example No. 1           | 5-19       |

| SATR Formats for Example No. 2           | 5-20       |

| Address Translation Example No. 2        | 5-21       |

| Relative PSA Assignments within an SE    |            |

| 9020 Addressing                          |            |

| Logical PSBAR Format                     | 5 24       |

| Setting of Physical PSBAR from           | 3-24       |

| Le rie-1 DCD A D                         | 5 95       |

| Logical PSBAR                            | 5-25       |

| Effective PSA Address Generation         | 5-26       |

| PSBAR Counter                            | 5-27       |

| Storing of Logical and Physical PSBAR    |            |

| PSA Example No. 1                        | 5-29       |

| PSA Example No. 2                        | 5-30       |

| 12 Field Definition for CE WRD           |            |

| Instruction                              | 6-2        |

| Instruction                              | 6-5        |

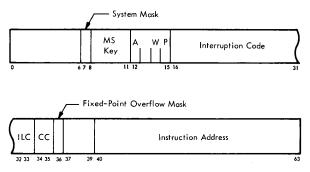

| CE Program Status Word Mask Bits         | 6-6        |

| Permanent Preferential Storage           | 00         |

| Assignments                              | 6.6        |

| CE Interrupt Actions                     | 0-0<br>∠ 0 |

| Abnormal Condition Monitoring and        | 0-0        |

|                                          | < 10       |

|                                          | 6-10       |

|                                          | 6-11       |

|                                          | 6-12       |

| Test and Set Example                     |            |

|                                          | 7-2        |

| Hardware-Generated External Interruption |            |

| Status Table                             | 7-3        |

| External Interrupt Handling              | 7-4        |

| Old PSW, Interruption Source             | 7-5        |

| Diagnose Accessible Register (DAR)       | 7-5        |

| Summary of Procedure for Handling        |            |

| External Interruption Signals            | 7-7        |

|                                          |            |

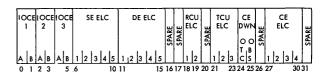

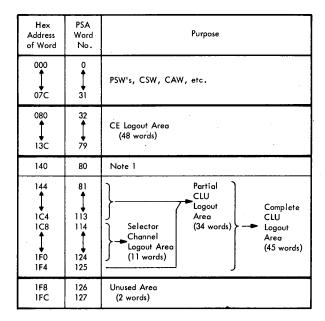

| PSA Logout Area Locations                | 8-2        |

9020 E Introduction (7/70) vii

| 8-2  | CE Error Handling 8-7                       | 8-11 |

|------|---------------------------------------------|------|

| 8-3  | CE Handling of SE Access Response           | 8-12 |

|      | Errors                                      | 8-13 |

| 8-4  | CE Handling of DE Access Errors 8-13        | 8-14 |

| 8-5  | CE Error Monitoring during Logout 8-14      | 8-15 |

| 8-6  | CE Handling of Internal Abnormal            | 8-16 |

|      | Conditions                                  | 9-1  |

| 8-7  | IOCE Handling of CLU Errors 8-17            | 9-2  |

| 8-8  | IOCE Handling of SE Access Response         | 9-3  |

|      | Errors 8-19                                 | 9-4  |

| 8-9  | IOCE Handling of Selector Channel           |      |

|      | Errors 8-22                                 | 9-5  |

| 8-10 | IOCE Handling of Abnormal Conditions . 8-23 |      |

|      |                                             | B-1  |

|      |                                             |      |

| SE Error Handling                    |    |  | 8-24 |

|--------------------------------------|----|--|------|

| DE Error Handling                    |    |  | 8-26 |

| TCU Error Handling                   |    |  | 8-27 |

| RCU Error Handling                   |    |  | 8-29 |

| RCU Abnormal Condition Handling      |    |  | 8-31 |

| DAU Error-Handling                   |    |  | 8-32 |

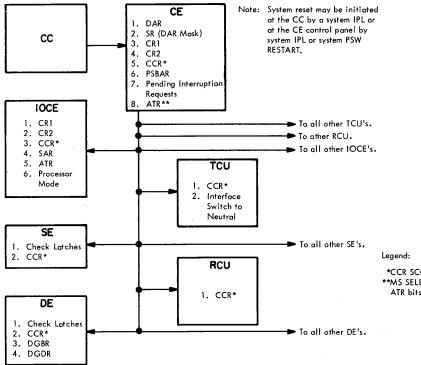

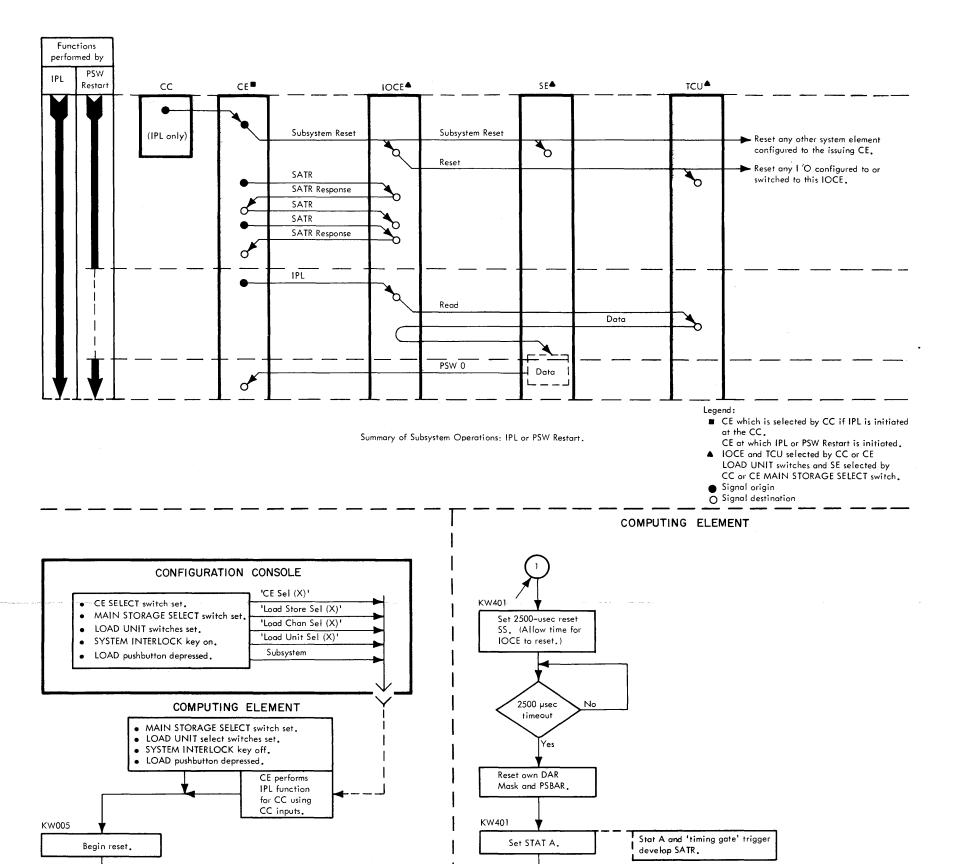

| IBM 9020E System Reset               |    |  | 9-2  |

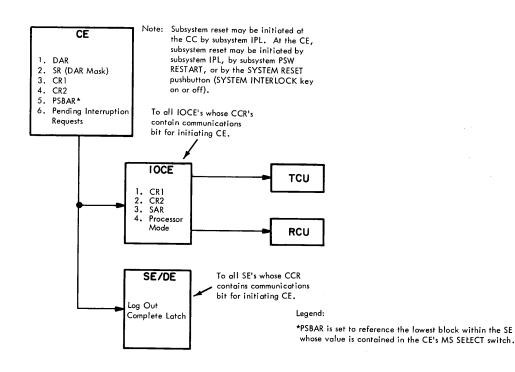

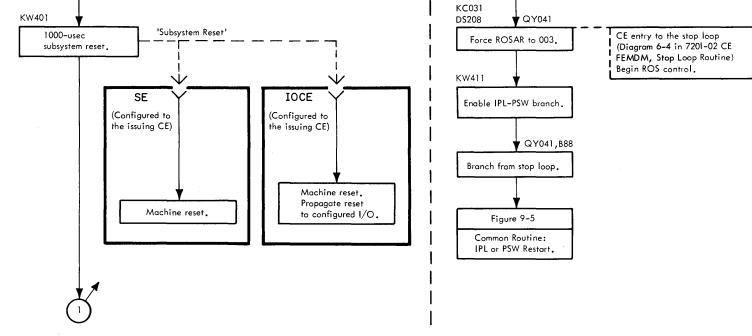

| IBM 9020E Subsystem Reset            |    |  | 9-2  |

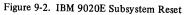

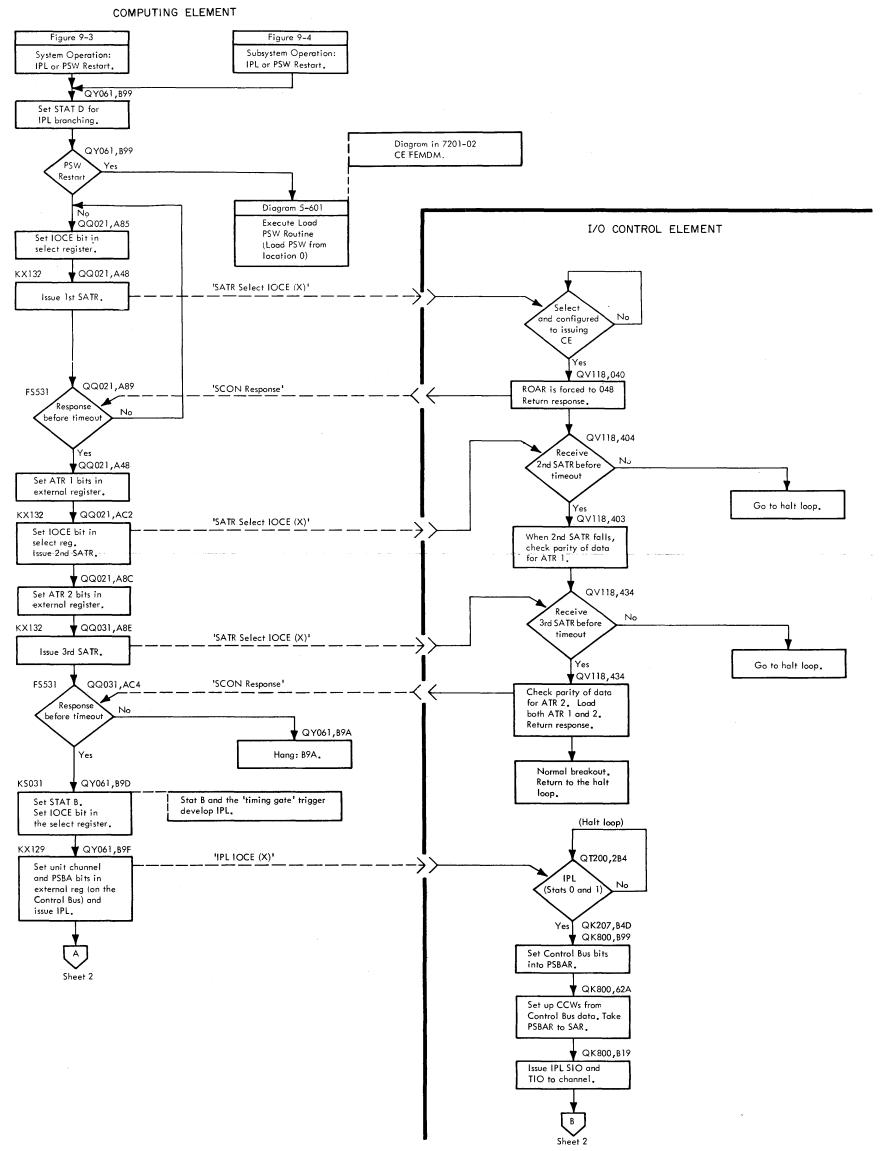

| System Operations, IPL or PSW Routin | ne |  | 9-5  |

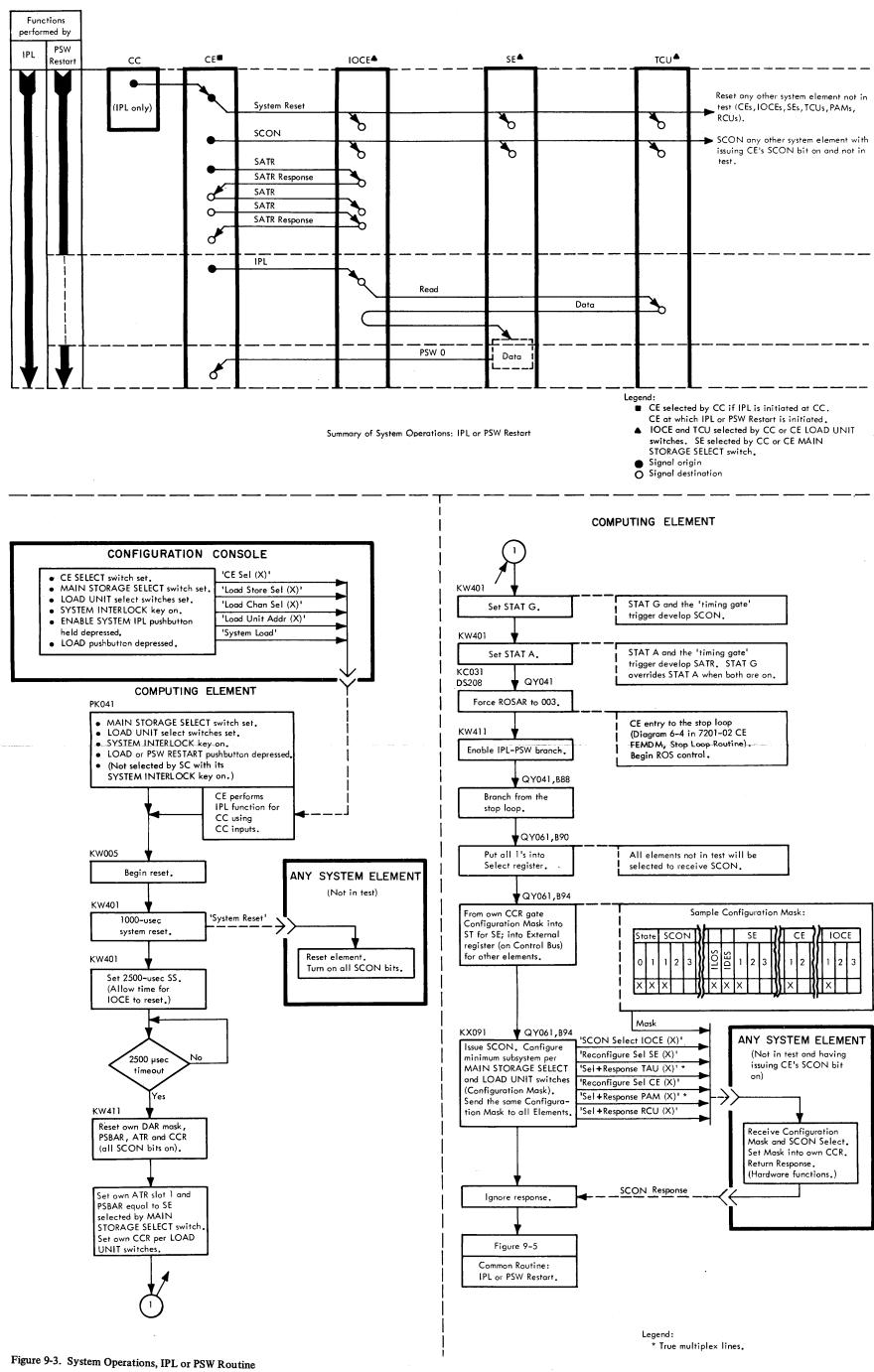

| Subsystem Operation, IPL or PSW      |    |  |      |

| Routine                              |    |  | 9-7  |

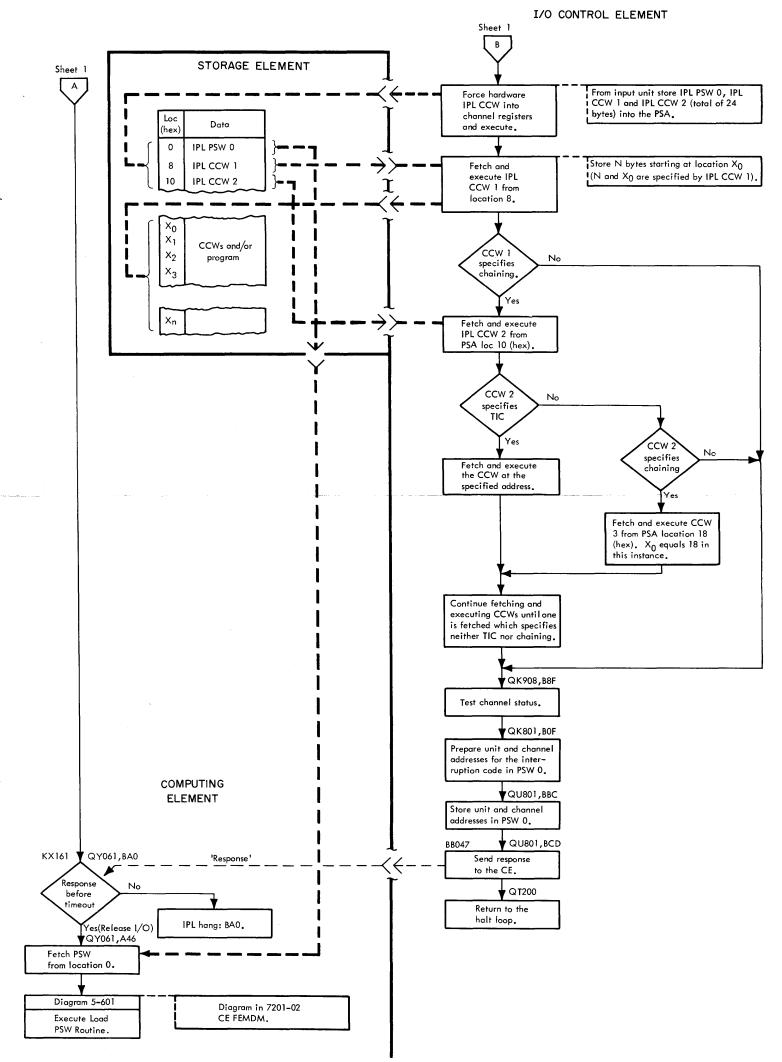

| Common Routine: IPL or PSW Restar    | rt |  |      |

| (2 Sheets)                           |    |  | 9-9  |

| Op Codes Not Executable in 360 Mode  |    |  |      |

| •                                    |    |  |      |

i

x (7/70)

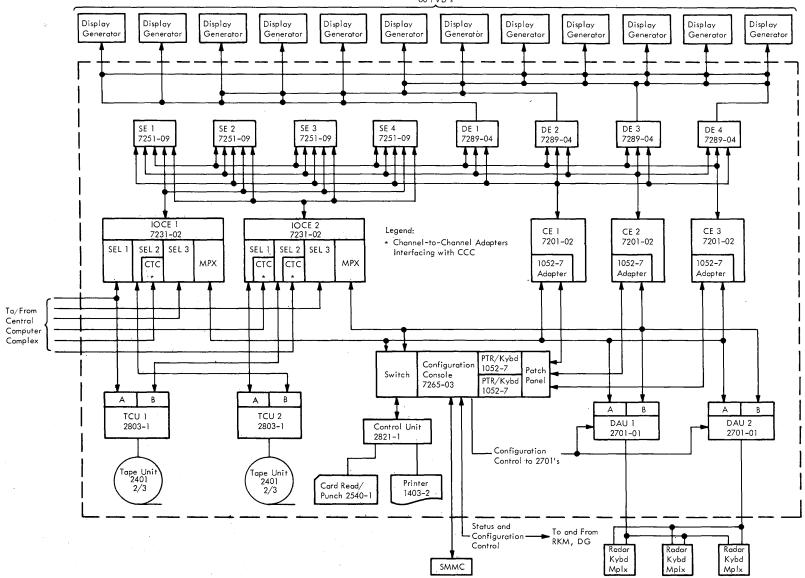

The IBM 9020E Display Channel Processor (DCP) System is an important part of the total complex of computers and computer-controlled equipment used in the air traffic control (ATC) task. The purpose of this equipment is to acquire accurate and adequate data and to present it for use by the flight controllers in real time. Figure 1-1 shows an overall view of this equipment complex, known as the National Airspace System (NAS) En Route Stage A, and illustrates the role of the 9020E system.

The overall ATC task includes a number of fairly distinct activities, some of which are listed below so that the role of the DCP system may be viewed in perspective:

- 1. Acquisition of input data directly from its source (flight plans, radar returns, weather information, etc.).

- 2. Processing of input data (sorting and formatting data, calculating flight paths and arrival times, etc.).

- 3. Production of flight progress strips.

- 4. Production and transmission of various operational messages (within the center, to other centers, to airports, etc.).

- 5. Production of bulk-processed radar data.

- 6. Storing of flight plans, flight progress records, weather information, etc.

- 7. Updating of stored information.

- 8. Final preparation of data for display.

- 9. Display of data for use by the flight controllers (radar data, tabular information, and weather information).

In addition to the ATC-related activities, the NAS complex provides facilities for monitoring its own operation. This enables changing traffic loads to be accommodated, malfunctions to be detected and isolated, and backup equipment to be called into operation when required. A NAS complex centers about a Central Computer Complex (CCC) which may be an IBM 9020A or 9020D system. Each performs the same functions, but the 9020D has higher speed and greater capacity than the 9020A.

Data from various sources, including digitized radar, teletype, IBM 1052 Printer/Keyboards, and flight data entry equipment, enters the NAS complex via adapters within the CCC which convert all incoming data to a code usable by the computer. This data is processed according to its type and source and is passed along to the appropriate output or is stored until needed.

Data leaves the CCC system as various types of operational messages, flight progress strips, and processed radar and weather information. The messages and flight strips are transferred from the CCC via adapters which translate them into the appropriate transmission code for the particular user. For example, messages to another center might be transmitted via teletype so that an adapter which translates from the computer code to the teletype code would be required.

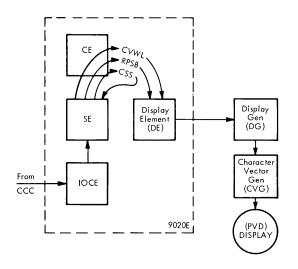

Processed radar and weather information leaves the CCC system via data channels that connect to the DCP system. The 9020E receives this data and continues to process it for display. This involves sorting the data, translating from co-ordinates on the earth to co-ordinates on the displays, and formatting the data so that it can be used by the display equipment. The incoming radar data is also processed according to type (beacon or primary), and the two are related to provide complete information on the display. Weather lines and tabular data are also prepared for display. Once the data is processed in this manner, the DCP system must interface with the display equipment so that the data can be transferred to the correct display efficiently and automatically.

Figure 1-1. Role of 9020E DCP in NAS En Route Stage A Complex

9020E Introduction (7/70) 1-1

Keyboards at each radar position enable the controllers to exercise control over the data displayed by requesting additional information, by updating information, and by requesting that tabular data on the display be moved. A "trackball" enables the controller to point out a specific target to the system. The keyboards and trackball are external to the DCP system, as are the displays. Thus, the DCP system has provisions for interfacing with this equipment and, when appropriate, can communicate data received from this source to the CCC system.

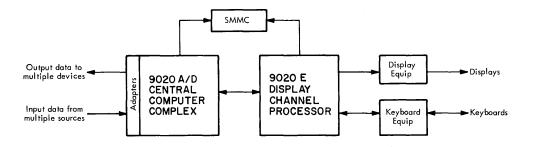

As can be seen from Figure 1-1 and the foregoing discussion, the 9020E DCP system provides the link between the CCC system and the display equipment. As the name Display Channel Processor implies, it is more than a channel for display data; it is also capable of processing that data and of buffering it for display. Further, it is capable of handling data returned from the controllers via the radar keyboards. This, then, is the role of the 9020E system in the total environment of IBM and non-IBM equipment that composes the NAS complex.

Two major interfaces enable the 9020E to link the CCC and the display equipment, namely, the DCP-CCC interface and the DCP-display equipment interface. The first of these represents an interface between two groups of IBM equipment; thus, it is similar to other interfaces internal to the CCC and DCP systems. This interface is the type that is used to attach input/output (I/O) equipment to computers in the IBM System/360 line and is referred to as the "standard I/O interface" in this manual. A summary of this standard interface is provided in Chapter 3.

DCP-display equipment interfacing consists of more than one interface. Separate interfaces exist for the transfer of display data, of radar keyboard data, and of control and configuration data. These interfaces are discussed more fully following discussions of system requirements and system elements which are basic to understanding the interfaces.

Note that both the CCC system and the DCP system interface with a System Maintenance Monitor Console (SMMC) which is external to both systems. The SMMC provides a central location from which maintenance personnel may monitor the overall operation of the NAS complex.

#### SYSTEM REQUIREMENTS

Because the NAS complex is engaged in the critical, real-time task of air traffic control, it is necessarily designed for maximum reliability. That is, the probability of the entire NAS complex being catastrophically rendered incapable of performing its mission is extremely low. Since all equipment is subject to failures to some extent, provision is made for failures so that they do not catastrophically interfere with the performance of the ATC task; this is

achieved partly through the use of highly reliable equipment and partly through a "fail-safe" and "fail-soft" approach. A fail-safe system is one that can perform its entire workload in the presence of any single element malfunction. A fail-soft system is one that is not completely crippled by the presence of a malfunction but, instead, performs only the essentials of its workload, delaying nonessential operations until later.

These concepts of reliability, fail-safe, and fail-soft, which are inherent in the NAS complex, are achieved within the 9020E system as a result of the following:

- 1. Equipment designed for maximum reliability and minimum downtime.

- 2. Battery backup power in all major elements which switches in automatically when there is a loss of external power.

- 3. Redundant (spare) elements provided for each major element.

- 4. The facility within each element to operate at various levels or states of operational capability.

- 5. The facility to dynamically reconfigure elements into subsystems which are appropriate to the current workload and which accommodate malfunctioning elements.

- 6. Elaborate facilities available to the program for monitoring malfunctions and abnormal conditions.

- 7. The capability of operating under a control program which can provide more rapid responses to changes in workload and system environment than could be provided by manual intervention.

These seven points are enlarged upon in the following text so that it can later be seen how the system requirements give rise to most of the hardware features of the 9020E system which are described in the remaining chapters of this manual.

The 9020E system comprises a number of elements, each of which is a solid-state device that provides high reliability. Elaborate parity-checking is incorporated so that errors may be detected. Downtime is minimized by the inclusion of maintenance features, at both the element and subsystem levels, which facilitate rapid isolation of failures. These features include maintenance panels for standalone testing, fault-location tests in some elements, and diagnostic programs for all elements and units.

Major elements in the DCP system are provided with battery backup power sources which can be automatically switched in when the element senses the loss of external power. Only major elements have this facility since loss of all power at a center results in loss of input data; hence, there is no need for peripheral I/O equipment. Further, loss of power to an individual piece of I/O equipment can be dealt with by substituting a redundant I/O device. However, unexpected loss of power to equipment in which the program is running is intolerable because no logical restarting point can be determined when power is restored. That is, there would be no way to determine what data had been processed and what had not. Extensive and timeconsuming reinitialization would be required.

The battery backup power source permits the program to continue operating for approximately 5 seconds after external power loss so that a logical stopping point (check point) can be established by the program. The system can then power down normally. When power is restored, processing can begin where it left off, with very little lost time.

Element redundancy is designed into the 9020E system so that more elements are available than are actually required for the performance of the ATC task. Some redundant elements may be failing elements which have been isolated from the system for maintenance, whereas others are "good" elements capable of being called into the ATC system. The recallable elements may be undergoing preventive maintenance or may be part of a subsystem involved in the maintenance of a particular element. They may also be engaged in the performance of non-ATC tasks, such as program debugging or the running of programs to perform a desired task not directly related to the ATC function.

Each element can operate in any one of four states of operational capability. The state of an element determines the degree of manual control which maintenance or operating personnel may exercise over it. For example, in state' 0 (the lowest operational state), virtually all element controls are operational so that maintenance may be performed on the element. In fact, by placing the element in Test mode, the ATC system will be denied use of the element completely. In state 3 (the highest operational state), virtually all manual controls are disabled so that the element can operate in the ATC system without interference. From the larger point of view, element state may be looked upon as the element's degree of availability to the ATC task.

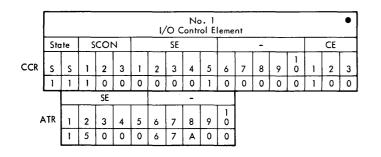

Each element has a configuration control register (CCR) which determines three things for it: (1) with which other elements in the system it may communicate, (2) what element state it is to assume, (3) which computing elements may change its configuration. The setting of these CCRs is under direct program control. Thus, it is possible for the program to alter the structure of the system as required. For example, if the traffic load increases, additional elements may be brought into the system; if an element fails, another element may be substituted.

To react to abnormal conditions, the program must be made aware of them. Elaborate monitoring facilities are built into the 9020E system. Provision is made to report the following to the program: logic checks, power checks, overtemperature conditions, the switching of an element to battery power, failure of an element to have valid data in its CCR, and the inability of an element to continue operation.

Most of the preceding text dealt with the manner in which various abnormal conditions are brought under program control and with the special facilities available to the program to respond to these conditions. All of this presupposes a running program that is capable of controlling the system. This brings us to the seventh point listed earlier.

The 9020E system is designed to operate under a control program (sometimes called a "monitor" or "supervisor"). The control program for the 9020 systems is called the executive control (EXC) program. Certain hardware implementation is provided specifically for the control program, e.g., certain instructions (called privileged instructions) are reserved for use only by this program.

As a result of these provisions, the EXC program may control the loading and execution of various subprograms; these subprograms run independently of the EXC program and of each other but may call upon the EXC program for various services. The EXC program is called via an "interruption" capability which is part of the 9020 architecture. This same interruption facility is used to inform the EXC program of various other exceptional or abnormal conditions such as the progress of an I/O operation or a malfunction in an element. This is discussed in further detail in Chapter 6.

In summary, the 9020E system is required to perform the ATC task of linking the CCC system and the display equipment in a reliable, fail-safe, and fail-soft manner. To accomplish this, the system is designed for reliability and quick repair, and is provided with battery backup and the ability to operate under a control program. The latter has available to it redundant elements which can be operated in four different operational states and which can be dynamically reconfigured to accommodate changing workload and malfunctions. Provision is made for the control program to monitor for malfunctions and other exceptional or abnormal conditions.

#### FUNCTION OF DCP SYSTEM ELEMENTS

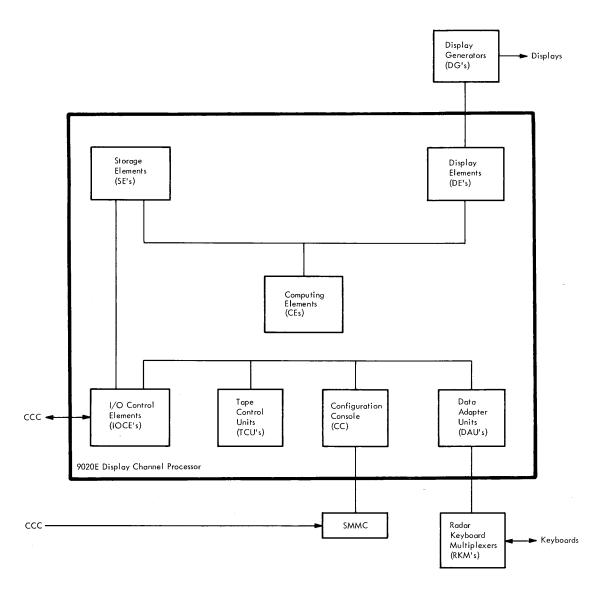

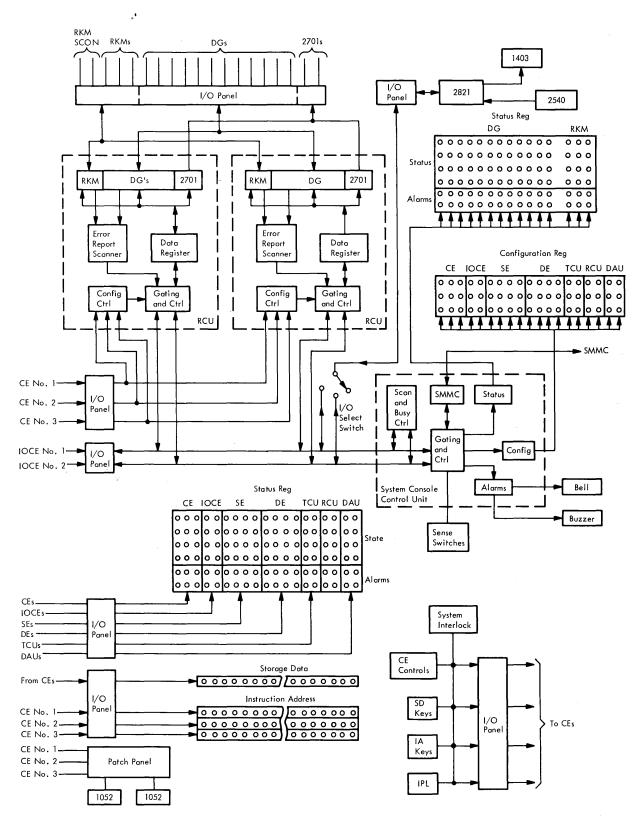

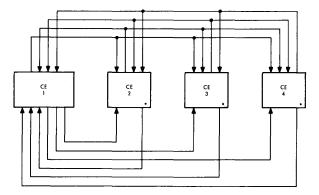

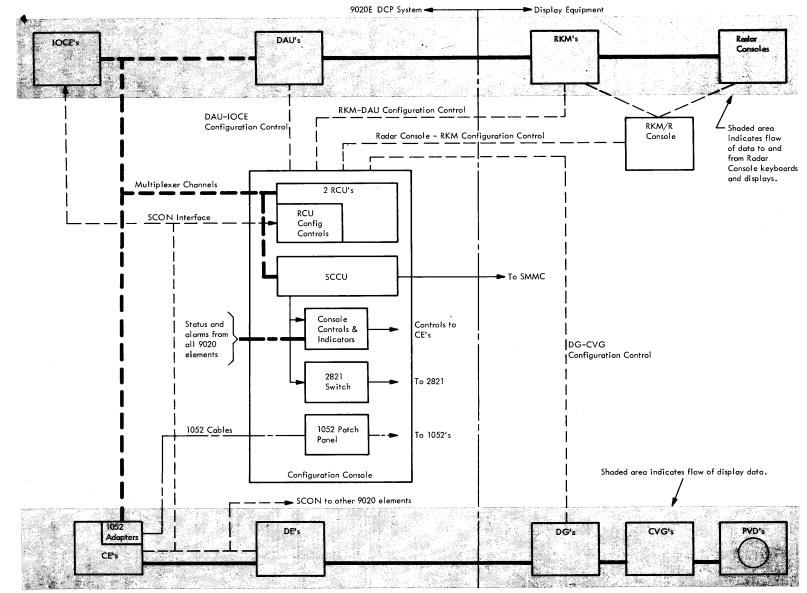

Figure 1-2 shows, in simplified form, the internal makeup of the 9020E system. Although the system contains redundant elements for most of the elements shown in Figure 1-2, only one of each type is shown for simplification.

The computing elements (CEs) form the nucleus of the system, providing the computational and logical capability necessary to execute programs and control the operation of other elements in the system. Though only major data interfaces are shown in Figure 1-2, note that the CEs

Figure 1-2. Function of DCP Elements

interface with almost every element in the system for configuration control and for error and abnormal condition monitoring.

As the prime element responsible for program execution (minor processing tasks can be delegated to the IOCE processors), a CE executes both the EXC program and the subprograms which accomplish the ATC task. These programs and the related data which they process are stored in Storage Elements (SEs). The CEs fetch instructions and data from the SEs and store the processed data back into the SEs.

The computing element in the 9020E system is provided with a class of instructions, called display instructions, which make possible rapid processing of the large amount of radar and weather information that enters the system from the CCC system.