# INTERDATA

# User's Manual

Publication Number 29-261R01

INFORMATION CONTAINED IN THIS MANUAL IS SUBJECT TO DESIGN CHANGE OR PRODUCT IMPROVEMENT

### **QUICK REFERENCE INDEX**

To aid in quickly locating a particular chapter, the index marks on the edge of this page are aligned with similar marks on the first page of each chapter.

| Chapter 1 | INTRODUCTION                                        | Y<br>À |

|-----------|-----------------------------------------------------|--------|

| Chapter 2 | PROCESSOR DESCRIPTION                               |        |

| Chapter 3 | DATA AND INSTRUCTION FORMATS AND STORAGE ADDRESSING | j.     |

| Chapter 4 | INSTRUCTION REPERTOIRE                              | ż      |

| Chapter 5 | INTERFACE DESIGN                                    |        |

| Chapter 6 | CONTROL CONSOLE                                     |        |

| Chapter 7 | INTERDATA SOFTWARE FAMILY                           |        |

| Chapter 8 | PERIPHERAL DEVICES AND MODULES                      | i i    |

| Chapter 9 | CONFIGURATION INSTALLATION PLANNING                 |        |

|           | APPENDICES                                          | 2      |

## **USER'S MANUAL**

# **TABLE OF CONTENTS**

| Chapter |      |          |                                                           | Page |

|---------|------|----------|-----------------------------------------------------------|------|

| 1       | INTR | ODUCTIO  | N                                                         | 1-1  |

|         | 1.1  | The INT  | TERDATA Family of Computers                               | 1-1  |

|         | 1.2  | System   | Description                                               | 1-2  |

|         |      | 1.2.1    | Memories                                                  | 1-2  |

|         |      | 1.2.2    | Direct Memory Access                                      |      |

|         |      | 1,2,3    | Selector Channel                                          |      |

|         |      | 1.2.4    | The Processor                                             |      |

|         |      | 1.2.5    | The Multiplexor Input/Out Bus                             | 1-3  |

|         | 1.3  | Periphe  | orals                                                     | 1-3  |

|         |      | 1.3.1    | Digital Multiplexor                                       | 1-3  |

|         |      | 1.3.2    | INTERTAPE Cassette System                                 | 1-4  |

|         |      | 1.3.3    | IBM Compatible Magnetic Tapes                             |      |

|         |      | 1.3.4    | Removable Cartridge Disc System                           | 1-4  |

|         |      | 1.3.5    | Magnetic Drum Storage System                              | 1-4  |

|         |      | 1.3.6    | Data Communications Equipment                             | 1-4  |

|         |      | 1.3.7    | High Speed Paper Tape System                              | 1-4  |

|         |      | 1.3.8    | System Modules                                            | 1-4  |

|         | 1.4  | Software | e                                                         | 1-4  |

|         |      | 1.4.1    | Assembler                                                 | 1-4  |

|         |      | 1.4.2    | Loader Descriptions                                       | 1-5  |

|         |      | 1.4.3    | Text Editor (TIDE)                                        | 1-5  |

|         |      | 1.4.4    | Debug (CLUB)                                              | 1-6  |

|         |      | 1.4.5    | FORTRAN (Models 70 and 80 only)                           | 1-6  |

|         |      | 1.4.6    | Basic Operating System (BOSS)                             | 1-6  |

|         |      | 1.4.7    | Real Time Operating System (RTOS) (Models 70 and 80 only) | 1-6  |

|         |      | 1.4.8    | Test Programs                                             | 1-6  |

|         | 1.5  | Custome  | er Support                                                | 1-6  |

|         |      | 1.5.1    | Computation Center Facilities                             | 1-6  |

|         |      | 1.5.2    | Field Service                                             | 1-7  |

|         |      | 1.5.3    | Training Center                                           | 1-7  |

|         |      | 1.5.4    | Systems Engineering and Programming                       | 1-7  |

|         |      | 1.5.5    | INTERCHANGE                                               | 1-7  |

| 2       | PROC | ESSOR DI | ESCRIPTION                                                | 2-1  |

|         | 2.1  | Micro-F  | Programmed INTERDATA Processor Architecture               | 2-1  |

|         | 2.2  | Process  | sor Block Diagram                                         | 2-1  |

|         | 2.3  | Process  | or Operation                                              | 2-3  |

|         |      | 2.3.1    | Program Status Words                                      | 2-3  |

|         |      | 2.3.2    | Instruction Execution                                     | 2-3  |

|         |      | 2.3.3    | Main Memory Allocation                                    | 2-4  |

|         |      |          |                                                           |      |

| Chapter |       |                                                                                                                                                                                                                                                                                                   | Page                                                              |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|         | 2.4   | Interrupt System                                                                                                                                                                                                                                                                                  | 2-6<br>2-6<br>2-7<br>2-8<br>2-10<br>2-19                          |

| 3       | DATA  | AND INSTRUCTION FORMATS AND STORAGE ADDRESSING                                                                                                                                                                                                                                                    | 3-1                                                               |

|         | 3.1   | Introduction                                                                                                                                                                                                                                                                                      | 3-1                                                               |

|         | 3.2   | Data Formats                                                                                                                                                                                                                                                                                      | 3-1<br>3-1<br>3-1<br>3-3<br>3-4                                   |

|         | 3.3   | Instruction Formats                                                                                                                                                                                                                                                                               | 3-5                                                               |

|         | 3.4   | General Register Usage                                                                                                                                                                                                                                                                            | 3-6                                                               |

|         | 3.5   | Storage Addressing                                                                                                                                                                                                                                                                                | 3-7                                                               |

| 4       | INSTR | UCTION REPERTOIRE                                                                                                                                                                                                                                                                                 | 4-1                                                               |

|         | 4.1   | Introduction                                                                                                                                                                                                                                                                                      | 4-1                                                               |

|         | 4.2   | Fixed-Point Load/Store Instructions 4.2.1 Load Halfword 4.2.2 Load Multiple 4.2.3 Store Halfword 4.2.4 Store Multiple                                                                                                                                                                             | 4-3<br>4-4<br>4-5<br>4-5<br>4-6                                   |

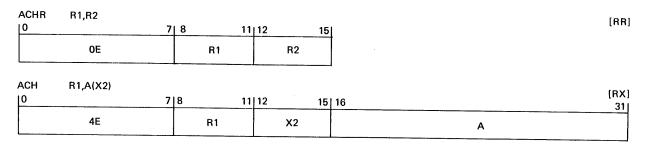

|         | 4.3   | Fixed-Point Arithmetic Instructions.  4.3.1 Add Halfword.  4.3.2 Add with Carry Halfword  4.3.3 Subtract Halfword.  4.3.4 Subtract with Carry Halfword  4.3.5 Compare Logical Halfword  4.3.6 Compare Halfword  4.3.7 Multiply Halfword  4.3.8 Multiply Halfword Unsigned  4.3.9 Divide Halfword. | 4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14<br>4-14 |

|         | 4.4   | Logical and Bit Manipulating Instructions 4.4.1 AND Halfword 4.4.2 OR Halfword 4.4.3 Exclusive OR Halfword 4.4.4 Test Halfword Immediate                                                                                                                                                          | 4-16<br>4-17<br>4-18<br>4-19<br>4-20                              |

| Chapter |      | Paş                                                       |

|---------|------|-----------------------------------------------------------|

|         | 4.5  | Byte Handling Instructions                                |

|         |      | 4.5.1 Load Byte                                           |

|         |      | 4.5.2 Store Byte                                          |

|         |      | 4.5.3 Exchange Byte                                       |

|         |      | 4.5.4 Compare Logical Byte                                |

|         | 4.6  | Shift/Rotate Instructions 4-2                             |

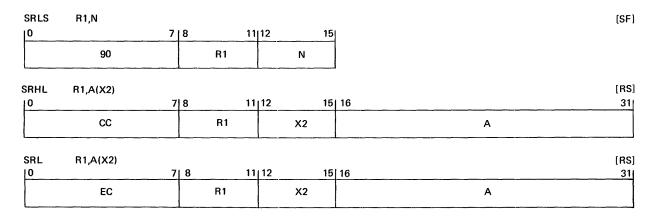

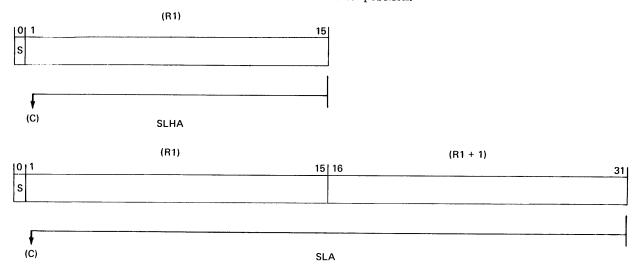

|         |      | 4.6.1 Shift Left Logical                                  |

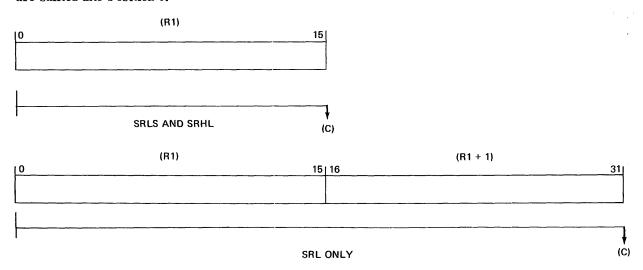

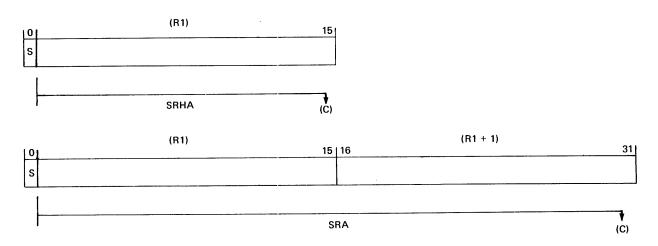

|         |      | 4.6.2 Shift Right Logical                                 |

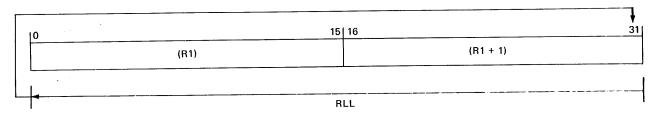

|         |      | 4.6.3 Rotate Left Logical                                 |

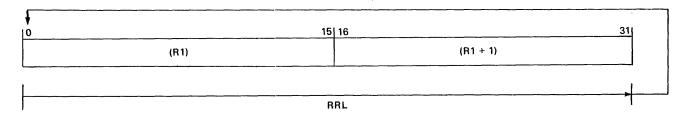

|         |      | 4.6.4 Rotate Right Logical 4-20                           |

|         |      | 4.6.5 Shift Left Arithmetic                               |

|         |      | 4.6.6 Shift Right Arithmetic                              |

|         | 4.7  | Branch Instructions                                       |

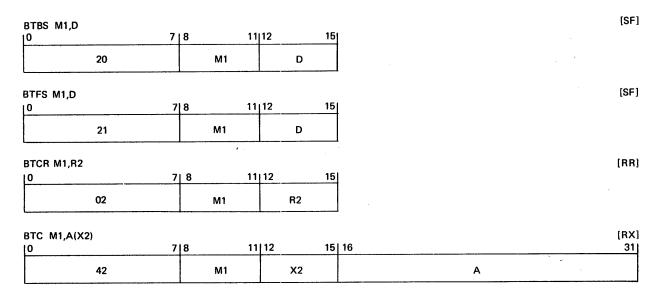

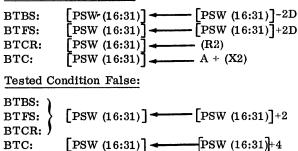

|         |      | 4.7.1 Branch on True Condition 4-3                        |

|         |      | 4.7.2 Branch on False Condition 4-3                       |

|         |      | 4.7.3 Branch on Index 4-3-                                |

|         |      | 4.7.4 Branch and Link                                     |

|         | 4.8  | Input/Output Instructions                                 |

|         | _•   | 4.8.1 Acknowledge Interrupt                               |

|         |      | 4.8.2 Sense Status                                        |

|         |      | 4.8.3 Output Command                                      |

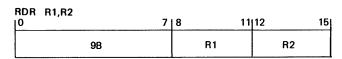

|         |      | 4.8.4 Read Data                                           |

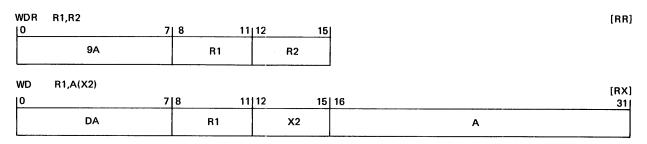

|         |      | 4.8.5 Write Data                                          |

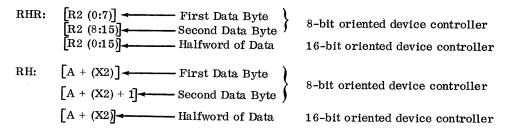

|         |      | 4.8.6 Read Halfword                                       |

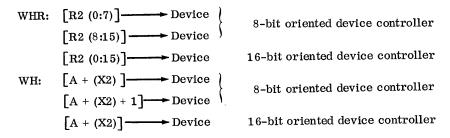

|         |      | 4.8.7 Write Halfword                                      |

|         |      | 4.8.8 Autoload                                            |

|         | 4.9  | Block Input/Output Instructions                           |

|         | 4.0  | 4.9.1 Read Block                                          |

|         |      | 4.9.2 Write Block                                         |

|         | 4 10 | Constant Control Trestonations                            |

|         | 4.10 | System Control Instructions                               |

|         |      | 4.10.1 Load Program Status Word                           |

|         |      | 4.10.2 Exchange Program Status                            |

|         |      | 4.10.3 Simulate Interrupt                                 |

|         |      | 4.10.4 Supervisor Call                                    |

|         | 4.11 | Floating-Point Instructions (Models 70 and 80 only) 4-5   |

|         |      | 4.11.1 Floating-Point Load 4-5                            |

|         |      | 4.11.2 Floating-Point Store                               |

|         |      | 4.11.3 Floating-Point Add                                 |

|         |      | 4.11.4 Floating-Point Subtract 4-53                       |

|         |      | 4.11.5 Floating-Point Compare 4-54                        |

|         |      | 4.11.6 Floating-Point Multiply 4-58                       |

|         |      | 4.11.7 Floating-Point Divide                              |

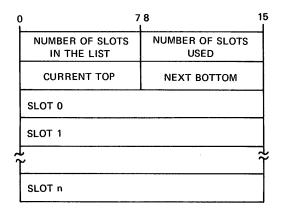

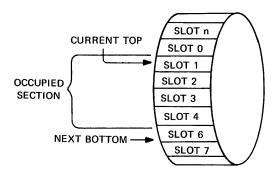

|         | 4.12 | List Processing Instructions (Models 70 and 80 only) 4-57 |

|         |      | 4.12.1 Add to Top/Bottom of List 4-58                     |

|         |      | 4.12.2 Remove From Top/Bottom of List                     |

| Chapter |      |                                                        | Page   |

|---------|------|--------------------------------------------------------|--------|

| 5       | INTE | ERFACE DESIGN                                          | 5-1    |

|         | 5.1  | Introduction                                           | . 5-1  |

|         | 5.2  | Systems Interface                                      | . 5-1  |

|         |      | 5.2.1 Multiplexor Channel                              | . 5-1  |

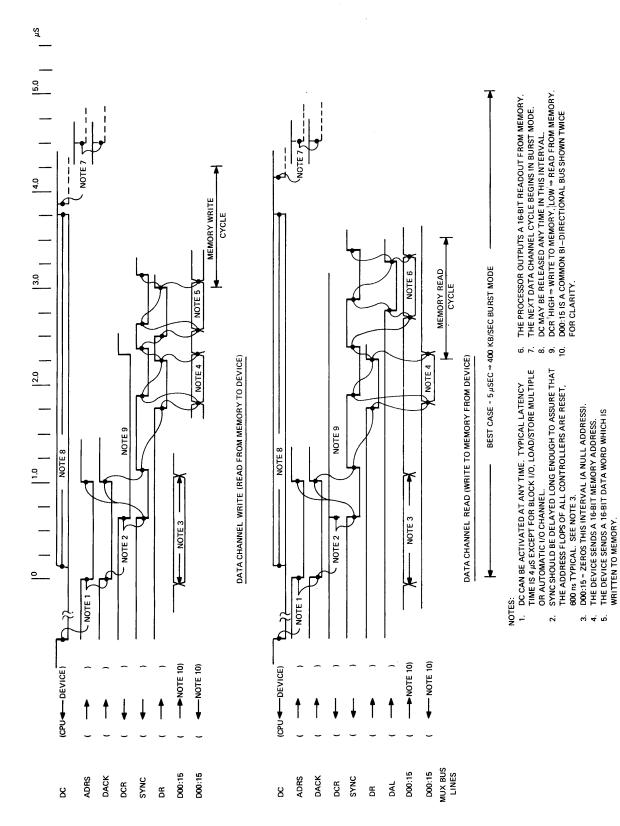

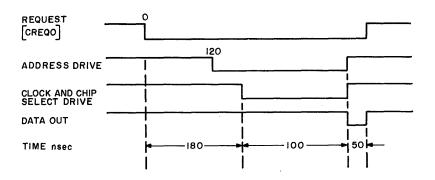

|         |      | 5.2.2 Interleaved Data Channel (Models 70 and 80 only) | . 5-5  |

|         | 5.3  | Device Controller Logic Design                         | . 5-5  |

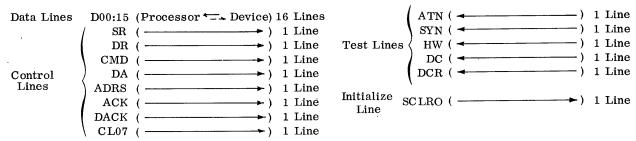

|         |      | 5.3.1 Multiplexor Bus                                  | . 5-5  |

|         |      | 5.3.2 Device Controller Addressing                     |        |

|         |      | 5.3.3 Data and Status Input                            | . 5-9  |

|         |      | 5.3.3.1 Data                                           |        |

|         |      | 5.3.3.2 Status                                         |        |

|         |      | 5.3.4 Data and Command Output                          |        |

|         |      | 5.3.4.1 Data                                           | . 5-12 |

|         |      | 5.3.4.2 Command                                        | . 5-12 |

|         |      | 5.3.5 Interrupt Control                                | . 5-12 |

|         |      | 5.3.6 Multiplexor Bus Wiring                           | . 5-15 |

|         |      | 5.3.7 Multiplexor Channel Timing                       | . 5-15 |

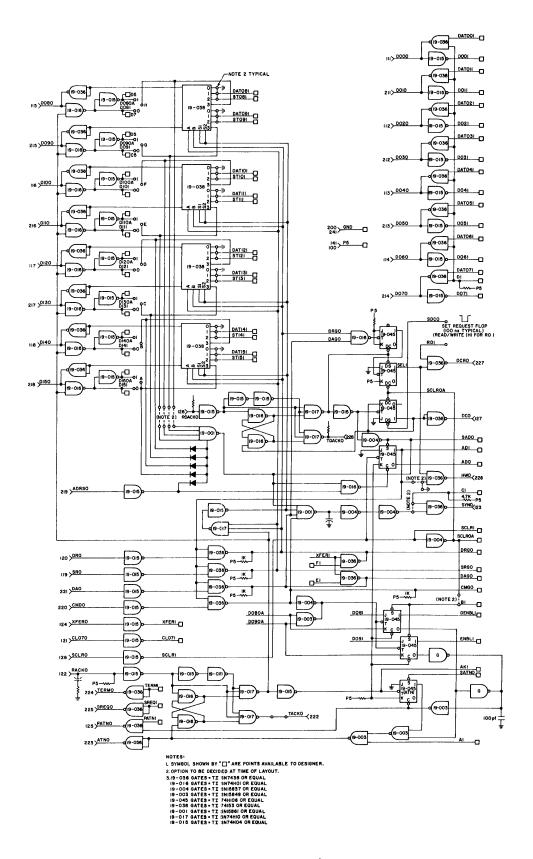

|         |      | 5.3.8 General Multiplexor Bus Interface                | . 5-18 |

|         |      | 5.3.9 Interleaved Data Channel Interface Design        | . 5-18 |

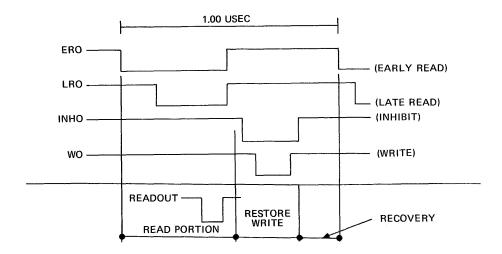

|         | 5.4  | Memory Bus                                             | . 5-23 |

|         |      | 5.4.1 Introduction                                     | . 5-23 |

|         |      | 5.4.2 Memory Bus Lines                                 | . 5-24 |

|         | 5.5  | Selector Channel                                       | . 5-29 |

|         | 5.6  | General Purpose Interface                              | . 5-33 |

|         |      | 5.6.1 Universal Interface Module                       |        |

|         |      | 5.6.2 General Purpose Interface Board                  | . 5-35 |

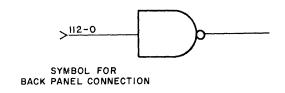

|         |      | 5.6.2.1 Component Field Numbering                      | . 5-35 |

|         |      | 5.6.2.2 Connector Layout                               | . 5-35 |

|         |      | 5.6.2.3 Available Cables                               | . 5-35 |

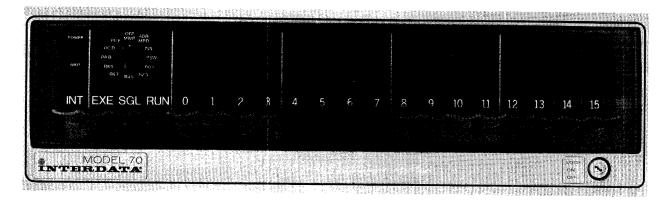

| 6       | CON  | TROL CONSOLE                                           | . 6-1  |

|         |      |                                                        | 2.1    |

|         | 6.1  | Introduction                                           | . 6-1  |

|         | 6.2  | Control Console Description                            | . 6-1  |

|         |      | 6.2.1 Key Operated Security Lock                       |        |

|         |      | 6.2.2 Control Switches                                 |        |

|         |      | 6.2.3 Function Switches                                | . 6-2  |

| Chapter |       |          |                                                | Page         |

|---------|-------|----------|------------------------------------------------|--------------|

|         | 6.3   | Control  | Console Operating Procedures                   | 6-3          |

|         |       | 6.3.1    | Power Up                                       | 6-3          |

|         |       | 6.3.2    | Power Down                                     | 6-5          |

|         |       | 6.3.3    | Program Loading                                | 6-5          |

|         |       | 6.3.4    | Program Execution                              | 6-6          |

|         |       | 6.3.5    | Program Termination                            | 6-7          |

|         |       | 6.3.6    | Manually Initiated Memory Operations           | 6-7          |

|         |       |          | 6.3.6.1 Memory Read                            | 6-7          |

|         |       |          | 6.3.6.2 Memory Write                           | 6-7          |

|         | 6.4   | Progran  | nming Considerations                           | 6-8          |

|         |       | 6.4.1    | Control Console I/O                            | 6-8          |

|         |       | 6.4.2    | Console Interrupt                              | 6-9          |

|         |       | 6.4.3    | Wait State                                     | 6-9          |

|         |       | 6.4.4    | Power Fail                                     | 6-9          |

|         |       |          |                                                |              |

| 7       | INTE  | RDATA SO | OFTWARE FAMILY                                 | 7-1          |

|         | 7.1   | Introduc | etion                                          | 7-1          |

|         | 7.2   | Compar   | ison of OS vs Stand-Alone Programs             | . 7-2        |

|         | 7.3   | Program  | n Preparation                                  | 7-3          |

|         |       | 7.3.1    | Programming in an Operating System Environment | 7-3          |

|         |       | 7.3.2    | Programming in a Stand-Alone Environment       | 7-7          |

|         | 7.4   | Progran  | mming Conventions                              | 7-9          |

|         | 7.5   | INTERD   | OATA Assembler Program                         | 7-9          |

|         |       | 7.5.1    | General Description                            | 7-9          |

|         |       | 7.5.2    | Assembly Procedures                            | 7-12         |

|         |       | 7.5.3    | Assembler Language                             | 7-13         |

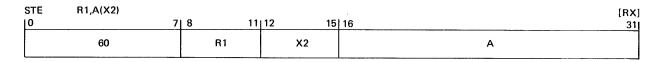

|         |       | 7.5.4    | Machine Instruction Format                     | 7-18         |

|         |       | 7.5.5    | Assembler Instructions (Pseudo Ops)            | 7-21         |

|         |       | 7.5.6    | Assembly Listing and Object Programs           | <b>7-3</b> 8 |

|         |       | 7.5.7    | Procedures for User-Defined Mnemonic Op-Codes  | 7-41         |

|         |       | 7.5.8    | Basic Assembler Operating Instructions         | 7-42         |

|         |       | 7.5.9    | OS Assembler Operating Instructions            | 7-51         |

|         | 7.6   | Assemb   | ly Level Programming Techniques                | 7-61         |

|         | 7.7   | FORTR    | AN IV                                          | 7-64         |

|         | • • • | 7.7.1    | General Description                            | 7-64         |

|         |       | 7.7.2    | FORTRAN Language Specifications                | 7-64         |

|         |       |          | Loading the FORTRAN Compiler                   | 7-65         |

|         |       | 7.7.3    | Memory Requirements                            | 7-67         |

|         |       | 7.7.4    | Compiler Execution Procedures                  | 7-69         |

|         |       | 7.7.5    | Loading a Compiled Program                     | 7-69         |

|         |       | 7.7.6    | roading a combined tradiam                     | . 00         |

| Chapter |      |           | Pa                                                          | ge         |

|---------|------|-----------|-------------------------------------------------------------|------------|

|         | 7.8  | Interact  | tive FORTRAN                                                | 70         |

|         |      | 7.8.1     | General Description                                         | 70         |

|         |      | 7.8.2     | Features                                                    | 72         |

|         |      | 7.8.3     | Use of the System                                           |            |

|         |      | 7.8.4     | System Capacity                                             | 73         |

|         | 7.9  | Loader 1  | Descriptions                                                | 74         |

|         |      | 7.9.1     | General                                                     | 74         |

|         |      | 7.9.2     | 50 Sequence Bootstrap Loader                                | 77         |

|         |      | 7.9.3     | Object Tape Format 7-8                                      |            |

|         |      | 7.9.4     | Features of the OS Library Loader 7-8                       |            |

|         |      | 7.9.5     | Features of Stand-Alone Loaders                             |            |

|         |      | 7.9.6     | General Loader Features                                     |            |

|         |      | 7.9.7     | Operation of Stand-Alone Loaders                            |            |

|         | 7.10 | Editor (7 | TIDE) Program                                               | 13         |

|         |      | 7.10.1    | Program Structure 7-9                                       |            |

|         |      | 7.10.2    | Operating Procedures                                        |            |

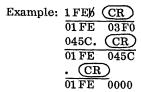

|         | 7.11 | Hexadec   | imal Debug (CLUB) Program                                   | 04         |

|         |      | 7.11.1    | Terminology 7-1                                             | 04         |

|         |      | 7.11.2    | Description of Operations                                   | .O=        |

|         |      | 7.11.3    | Bias Definition                                             | .05<br>.05 |

|         |      | 7.11.4    | Cell Examination and Modification                           | 00         |

|         |      | 7.11.5    |                                                             |            |

|         |      | 7.11.6    | Program Control         7-1           Utilities         7-1 |            |

|         |      | 7.11.7    | Operating Procedures                                        | 15         |

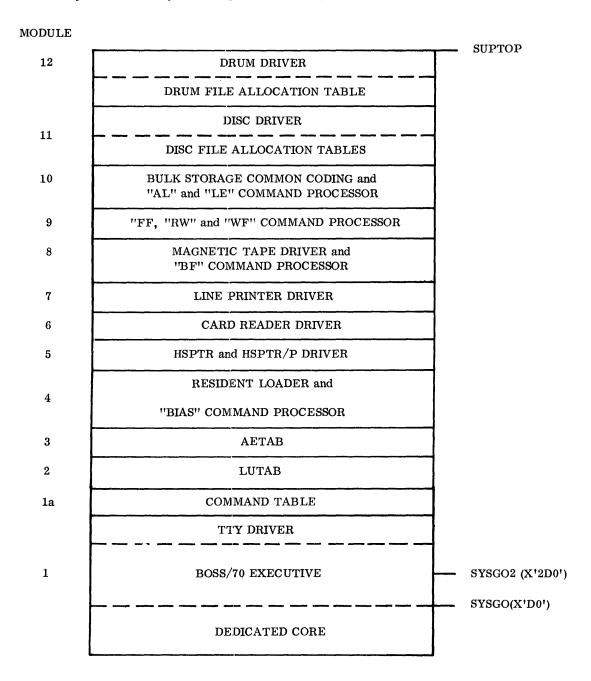

|         | 7.12 | Basic On  | perating System                                             | 10         |

|         |      | 7.12.1    | General Description                                         | 18         |

|         |      | 7.12.2    | Operational Characteristics                                 | 18         |

|         |      | 7.12.3    |                                                             |            |

|         |      | 7.12.4    | Programmable Commands                                       | 19         |

|         |      | 7.12.5    | Operator Commands                                           |            |

|         |      | 12.0      | System Configuration                                        | 20         |

|         | 7.13 |           | erating System 7-1                                          |            |

|         |      | 7.13.1    | Introduction                                                |            |

|         |      | 7.13.2    | Features                                                    |            |

|         |      | 7.13.3    | Description                                                 | 22         |

|         |      | 7.13.4    | DOS Programmable Commands                                   | 23         |

|         |      | 7.13.5    | DOS Operator Commands                                       | 24         |

|         |      | 7.13.6    | Configuration                                               | 25         |

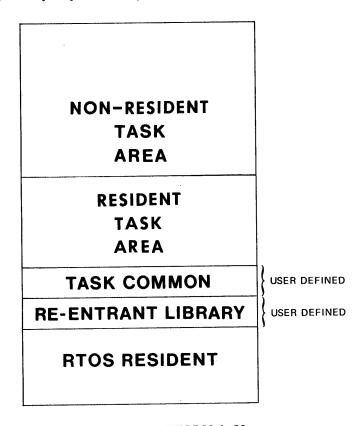

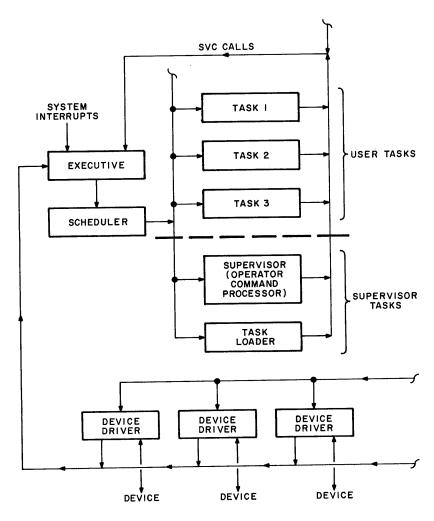

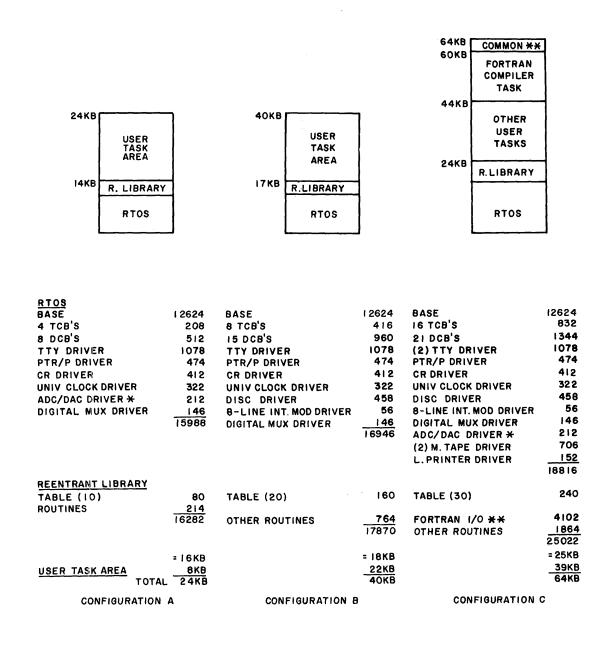

|         | 7.14 |           | ne Operating System                                         | 25         |

|         |      | 7.14.1    | Introduction                                                | 25         |

|         |      | 7.14.2    | Features and Characteristics                                |            |

|         |      | 7.14.3    | System Concepts                                             | 26         |

|         |      | 7.14.4    | System Organization                                         | 29         |

| Chapter |      |          |                                        | Page        |

|---------|------|----------|----------------------------------------|-------------|

| 8       | PERI | PHERAL   | DEVICES AND MODULES                    | 8-1         |

|         | 8.1  | Introdu  | ction                                  | 8-1         |

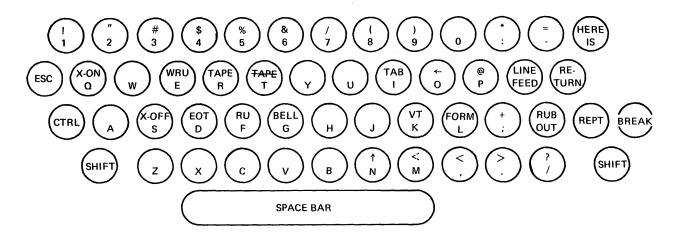

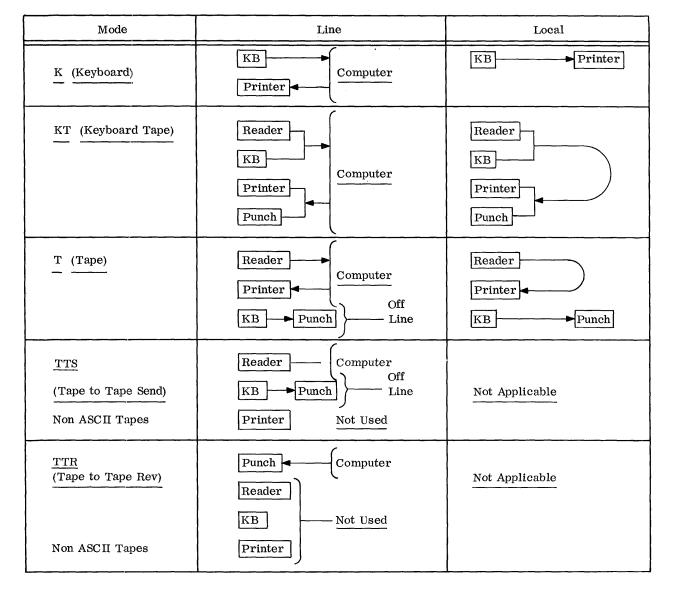

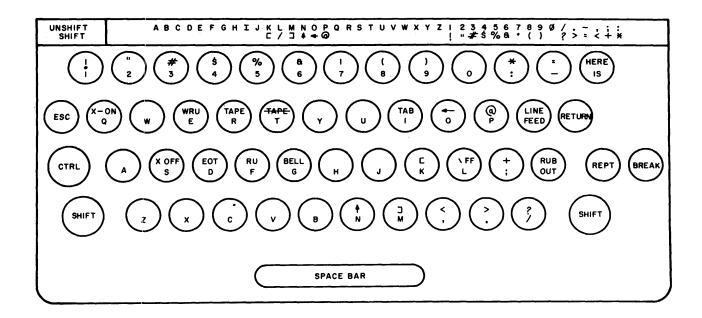

|         | 8.2  | Teletyp  | pewriters                              | 8-1         |

|         |      | 8.2.1    | Introduction                           | 8-1         |

|         |      | 8.2.2    | Configuration                          | 8-2         |

|         |      | 8.2.3    | Operating Procedures                   | 8-2         |

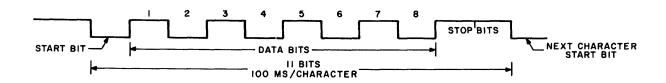

|         |      | 8.2.4    | Data Format                            | 8-4         |

|         |      | 8.2.5    | Programming Instructions               | 8- <b>5</b> |

|         |      | 8.2.6    | Programming Sequences                  | 8-7         |

|         |      | 8.2.7    | Interrupts                             | 8-8         |

|         |      | 8.2.8    | Initialization                         | 8-8         |

|         |      | 8.2.9    | Device Number                          | 8-11        |

|         |      | 0.2.9    | Device Number                          | 9-11        |

|         | 8.3  | High Sp  | eed Paper Tape Reader/Punch (HSPTR)    | 8-11        |

|         |      | 8.3.1    | General Description                    | 8-11        |

|         |      | 8.3.2    | Status and Command                     | 8-12        |

|         |      | 8.3.3    | Interrupts                             | 8-13        |

|         |      | 8.3.4    | Initialization                         | 8-13        |

|         |      | 8.3.5    | Device Number                          | 8-13        |

|         | 8.4  | Card Re  | eader                                  | 8-14        |

|         | 0.4  | 8.4.1    | General Description                    | 8-14        |

|         |      | 8.4.2    | Operator Controls                      | 8-14        |

|         |      | 8.4.3    | Status Indicator Lights                | 8-14        |

|         |      | 8.4.4    | Status and Command Bytes               | 8-15        |

|         |      | 8.4.5    |                                        | 8-15        |

|         |      | 8.4.6    | Data Format                            | 8-15        |

|         |      | 8.4.7    | Initialization                         | 8-15        |

|         |      | 8.4.8    | Operator Procedures                    | 8-15        |

|         |      | 8.4.9    | Programming                            | 8-17        |

|         | 0 =  | <u> </u> | 11 G 4 11 B: 'G 4                      |             |

|         | 8.5  |          | ble Cartridge Disc System              | 8-18        |

|         |      | 8.5.1    | General Description                    | 8-18        |

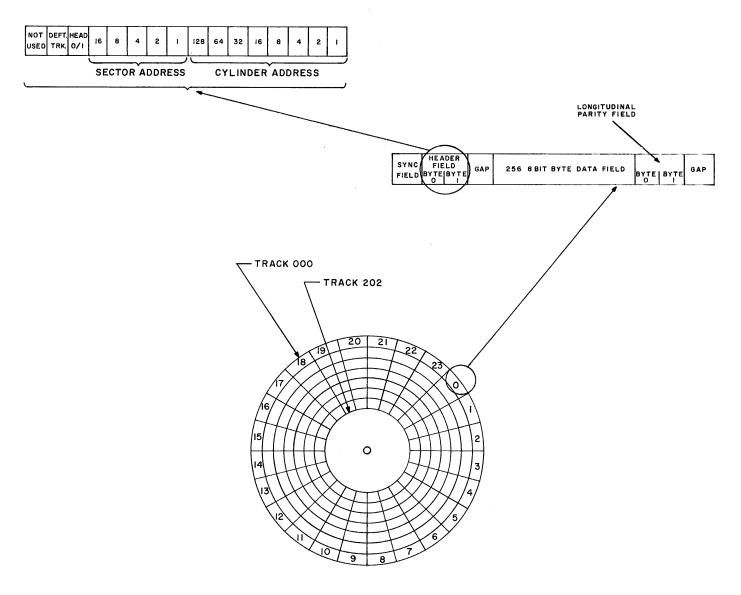

|         |      | 8.5.2    | Operational Characteristics            | 8-18        |

|         |      | 8.5.3    | Disc Format                            | 8-18        |

|         |      | 8.5.4    | Data Transfers                         | 8-19        |

|         |      | 8.5.5    | Specifications                         | 8-20        |

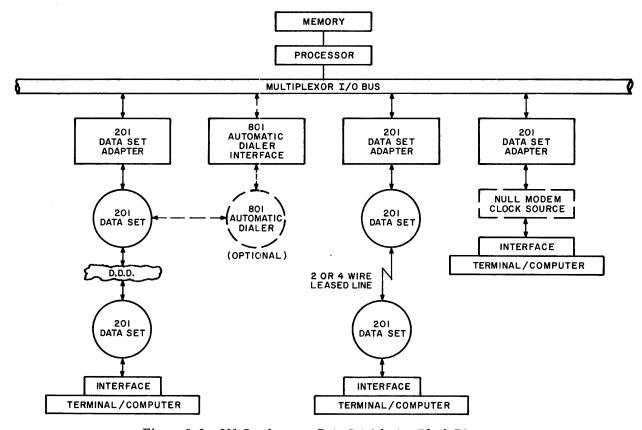

|         | 8.6  | 201 Sync | chronous Data Set Adapter              | 8-22        |

|         |      | 8.6.1    | General Description                    | 8-22        |

|         |      | 8.6.2    | Operational Characteristics            | 8-22        |

|         |      | 8.6.3    | Specifications                         | 8-23        |

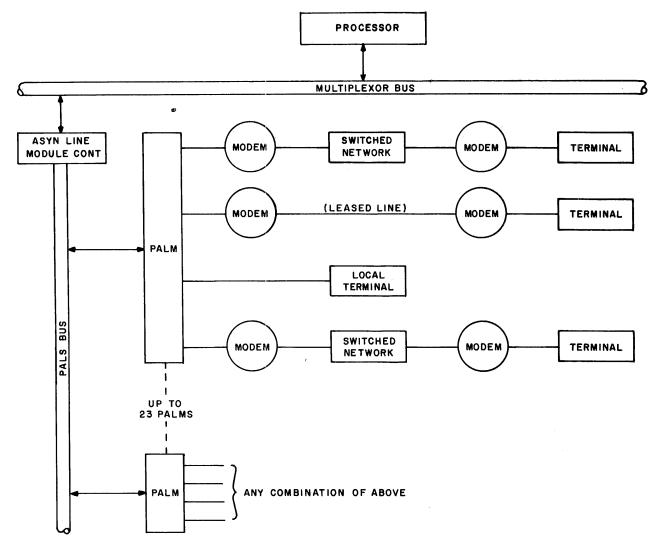

|         | 8.7  | Progran  | mmable Asynchronous Line System (PALS) | 8-24        |

|         |      | 8.7.1    | Introduction                           | 8-24        |

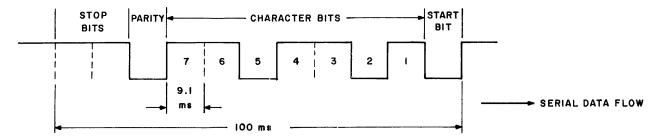

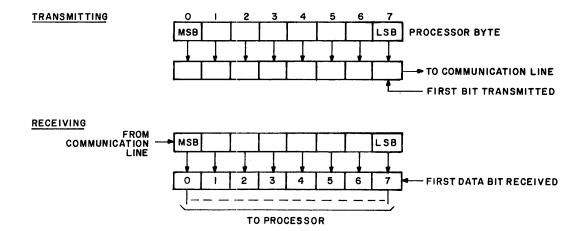

|         |      | 8.7.2    | Data Format                            | 8-25        |

|         |      | 8.7.3    | Programming Instructions               | 8-27        |

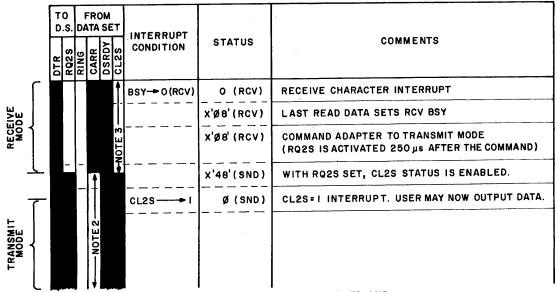

|         |      | 8.7.4    | Programming Sequences                  | 8-33        |

|         |      | 8.7.5    | Interrupts                             | 8-34        |

|         |      | 8.7.6    | Initialization                         | 8-35        |

|         |      | 8.7.7    | Device Number                          | 8-35        |

|         |      |          |                                        |             |

| Chapter |      |                                                         | Page       |

|---------|------|---------------------------------------------------------|------------|

|         | 8.8  | INTERTAPE Cassette System                               | 8-36       |

|         |      | 8.8.1 Specifications                                    | 8-36       |

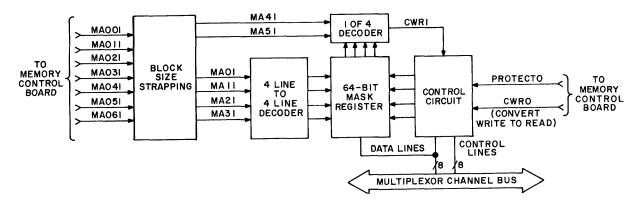

|         | 8.9  | Automatic Memory Protect Controller                     | 8-37       |

|         | 0.0  | 8.9.1 General Description                               | 8-37       |

|         |      | 8.9.2 Operational Characteristics                       | 8-37       |

|         |      | 8.9.3 Specifications                                    | 8-38       |

|         |      |                                                         |            |

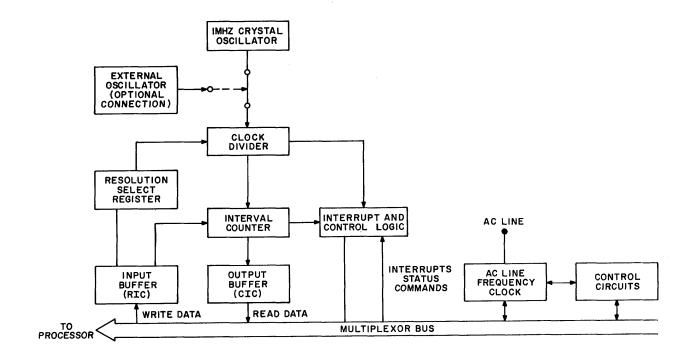

|         | 8.10 | Universal Clock Module                                  | 8-39       |

|         |      | 8.10.1 General Description                              | 8-39       |

|         |      | 8.10.2 Operational Characteristics                      | 8-39       |

|         |      | 8.10.3 Specifications                                   | 8-40       |

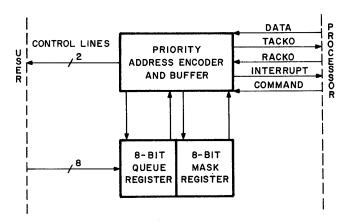

|         | 8.11 | The Eight Line Interrupt Module                         | 8-41       |

|         |      | 8.11.1 General Description                              | 8-41       |

|         |      | 8.11.2 Operational Characteristics                      | 8-41       |

|         |      | 8.11.3 Specifications                                   | 8-42       |

|         | 0.10 | Canial Line Duinter                                     | 0.46       |

|         | 8.12 | Serial Line Printer                                     | 8-42       |

|         |      | 8.12.1 General Description                              | 8-42       |

|         |      | 8.12.2 Operational Characteristics                      | 8-42       |

|         |      | 8.12.3 Specifications                                   | 8-43       |

|         | 8.13 | Loader Storage Unit (Model Numbers M70-104, M70-105)    | 8-43       |

|         |      | 8.13.1 Summary                                          | 8-43       |

|         |      | 8.13.2 Functional Description                           | 8-44       |

|         |      | 8.13.3 Applicable Processors                            | 8-44       |

|         |      | 8.13.4 Ordering Procedure                               | 8-44       |

|         | 8.14 | Automatic Loader for Basic Model 74 (Model No. M74-101) | 8-44       |

|         | 0.14 | 8.14.1 Summary                                          | 8-44       |

|         |      | 8.14.2 Functional Description                           | 8-44       |

|         |      |                                                         |            |

|         | 8.15 | Selector Channel                                        | 8-45       |

|         |      | 8.15.1 General Description                              | 8-45       |

|         |      | 8.15.2 Programming Instructions                         | 8-45       |

|         |      | 8.15.3 Programming Sequences                            | 8-46       |

|         |      | 8.15.4 Interrupts                                       | 8-49       |

|         |      | 8.15.5 Initialization                                   | 8-49       |

|         |      | 8.15.6 Device Number                                    | 8-49       |

|         |      | 8.15.7 Sample Program                                   | 8-50       |

| 9       | CONF | GURATION INSTALLATION PLANNING                          | 9-1        |

|         | 9.1  | Introduction                                            | 9-1        |

|         | 9.2  | Integrated Circuit Boards                               | 9-1        |

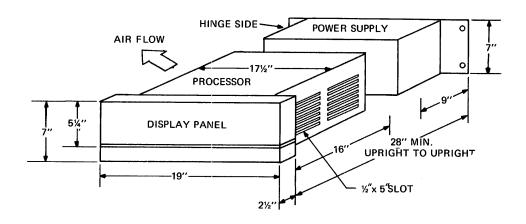

|         | 9.3  | Basic Processor Chassis                                 | 9-2        |

|         | 9.4  | System Fynansion Chassis                                | 9-3        |

|         | J. 4 | System Expansion Chassis                                | 9-3<br>9-3 |

|         |      | 9.4.2 10 Inch System Expansion Chassis                  | 9-3<br>9-3 |

|         |      | J. T. G. IV HICH DYSICHI L'ADAHSIUH CHASSIS             | უ−ა        |

| Chapter     |                                                    | Page              |

|-------------|----------------------------------------------------|-------------------|

|             | 9.5 Circuit Board Distribution                     | 9-3               |

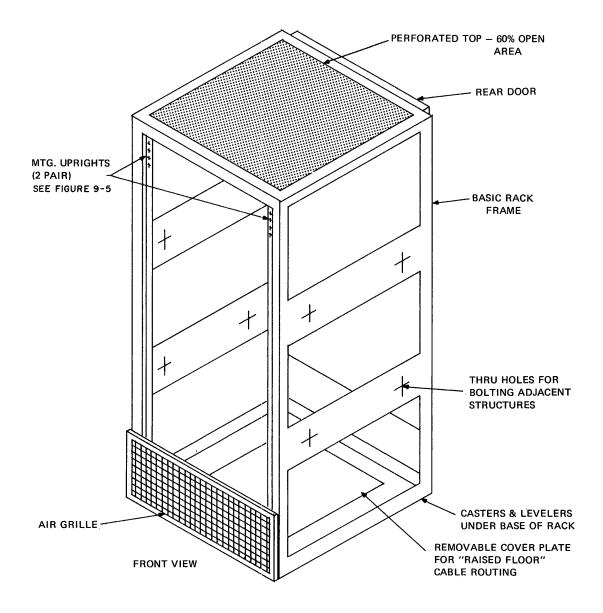

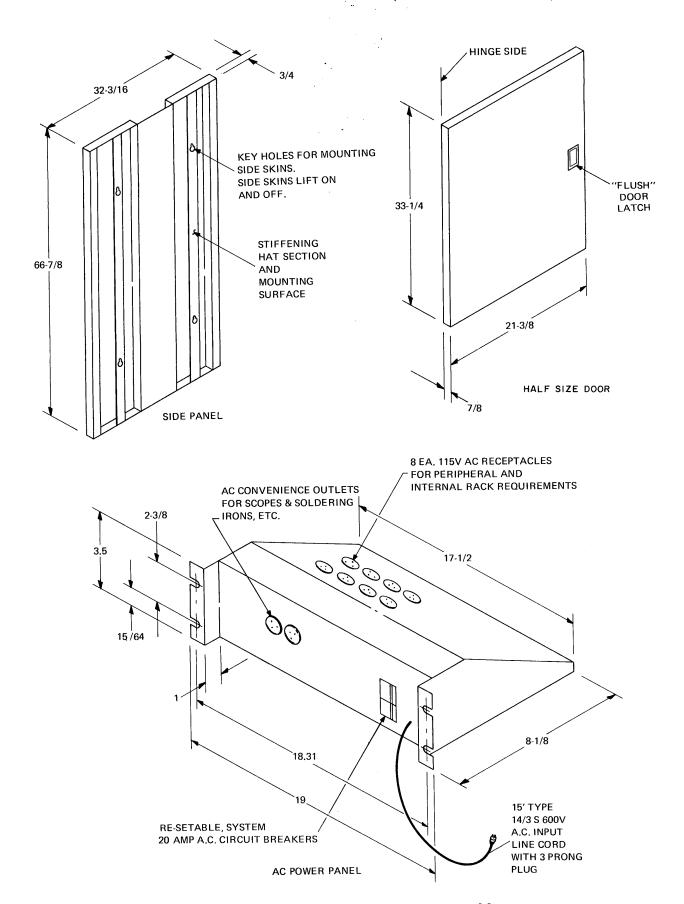

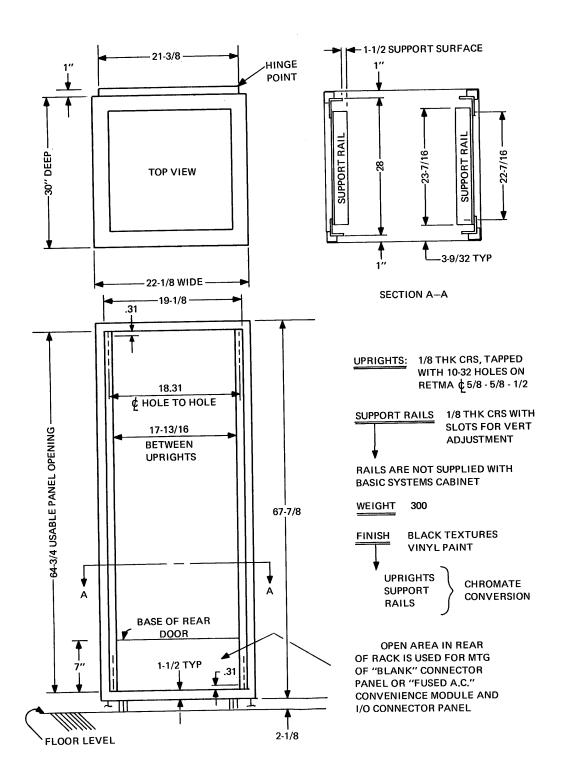

|             | 9.6 System Cabinets                                | 9-4               |

|             | 9.7 System Configuration Data                      | 9-8<br>9-8<br>9-9 |

|             | APPENDICES                                         |                   |

| Appendix    |                                                    |                   |

| 1           | INSTRUCTION SUMMARY - ALPHABETICAL                 | A1-1              |

| 2           | INSTRUCTION SUMMARY - NUMERICAL                    | A2-1              |

| 3           | EXTENDED BRANCH MNEMONICS                          | A3-1              |

| 4           | OP CODE MAP                                        | A4-1              |

| 5           | INSTRUCTION EXECUTION TIMES                        | A5-1              |

| 6           | AUTOMATIC I/O OPERATION AND TIMING DATA            | A6-1              |

| 7           | I/O REFERENCES                                     | A7-1              |

| 8           | ARITHMETIC REFERENCES                              | A8-1              |

| 9           | GLOSSARY OF TERMS                                  | A9-1              |

|             | ILLUSTRATIONS                                      |                   |

| Figure      |                                                    |                   |

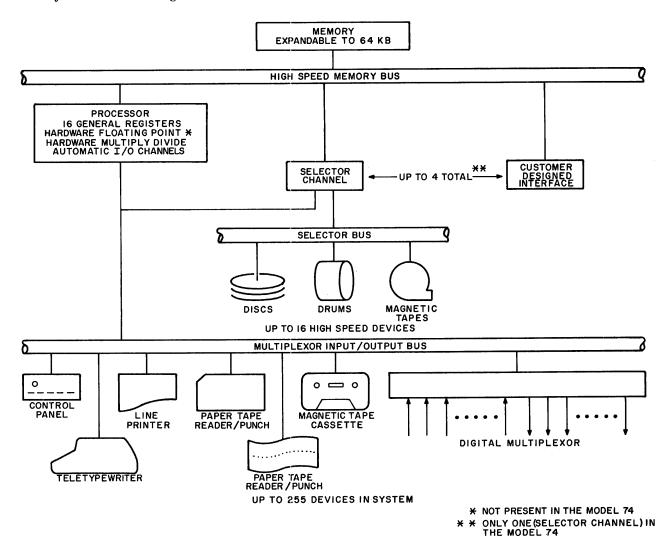

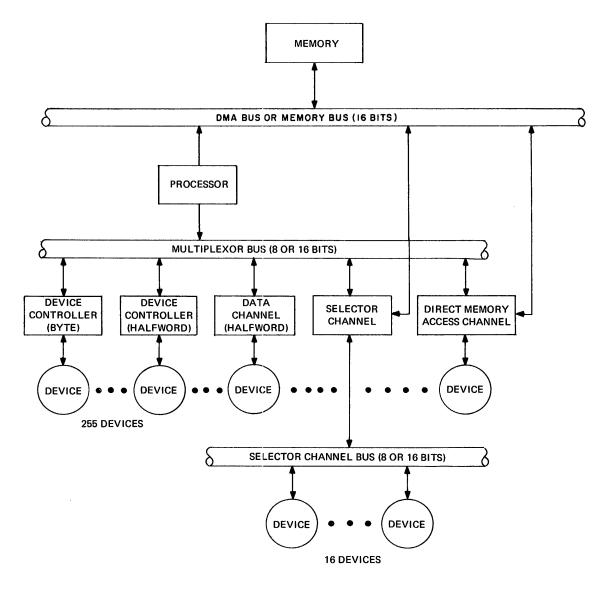

| 1-1         | System Block Diagram                               | 1-2               |

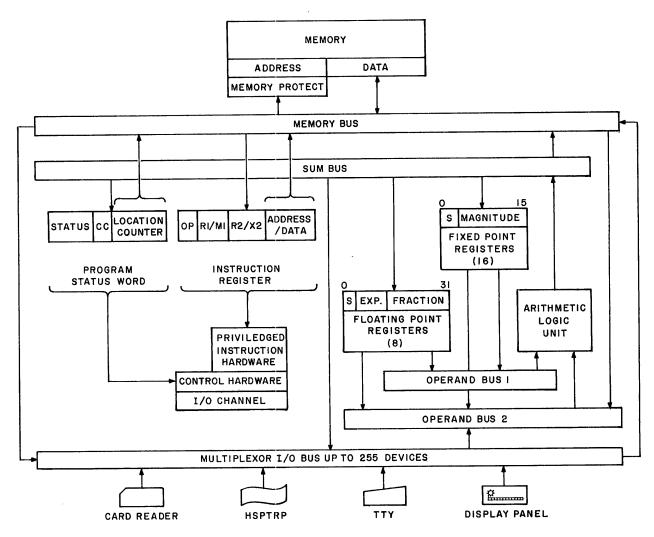

| 2-1         | Processor Block Diagram                            | 2-2               |

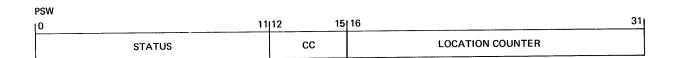

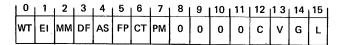

| 2-2         | Program Status Word Format                         | 2-2               |

| 2-3         | Program Status Bits                                | 2-3               |

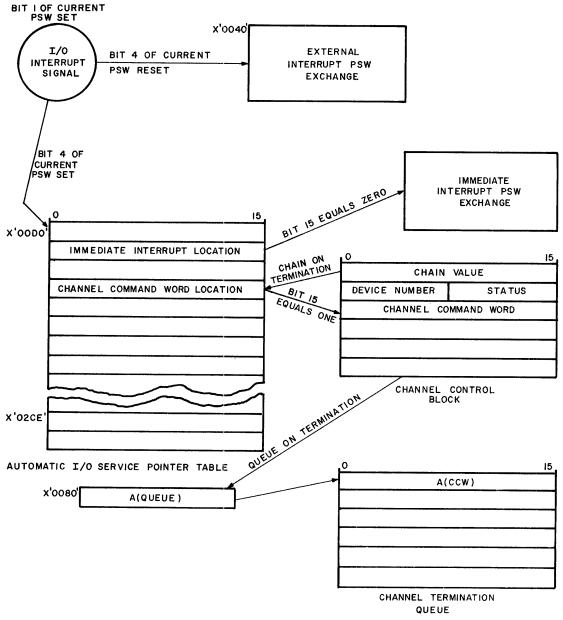

| 2-4         | I/O Channel Operation Block Diagram                | 2-10              |

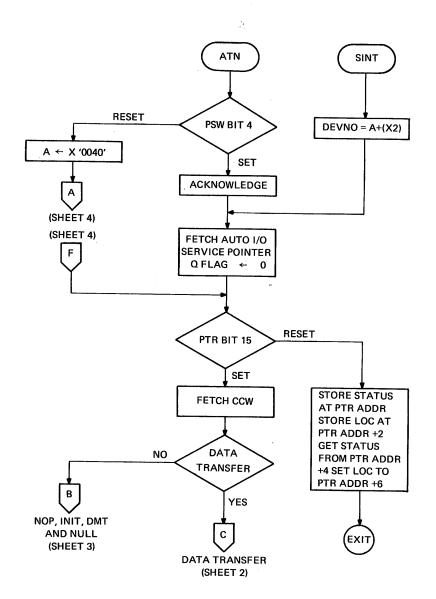

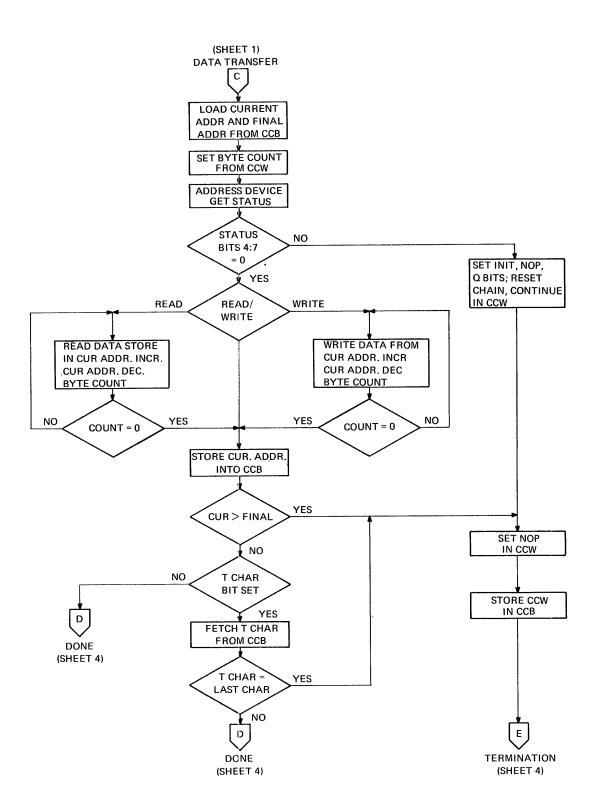

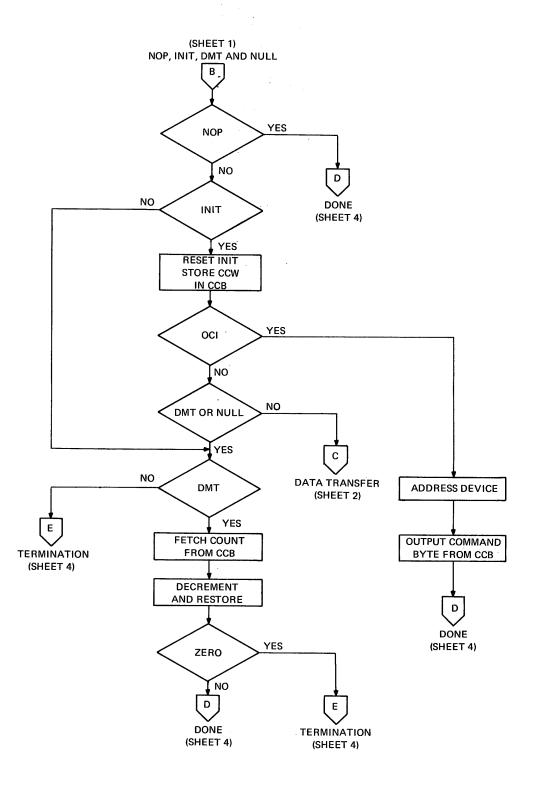

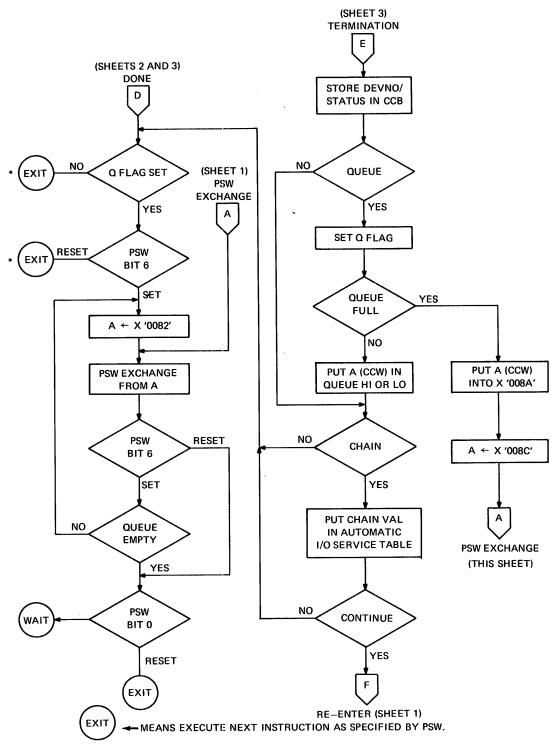

| 2-5         | Automatic Interrupt Service                        | 2-11              |

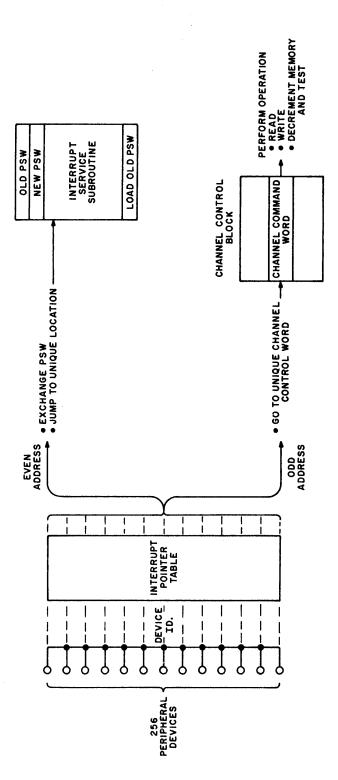

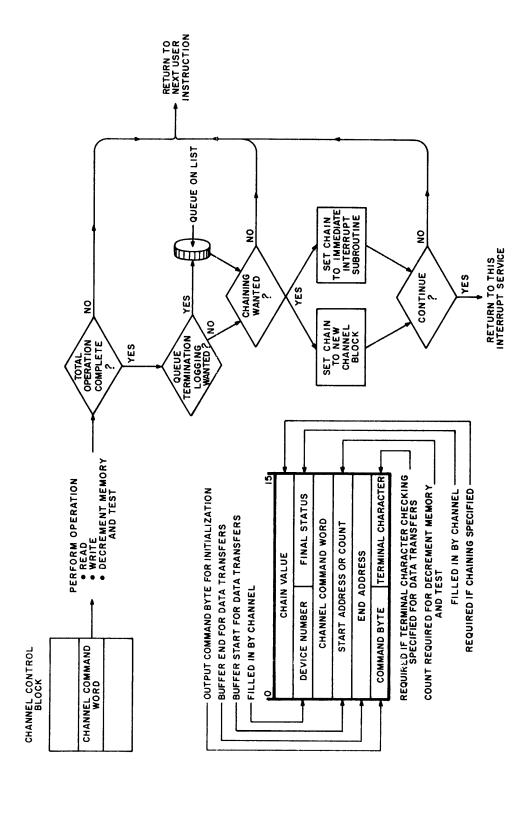

| 2-6         | Channel Control Block Diagram                      | 2-12              |

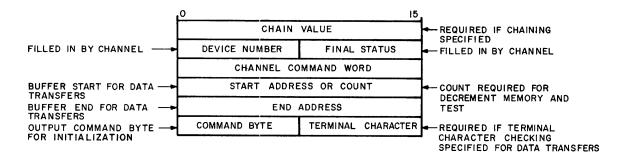

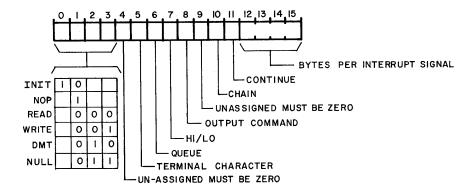

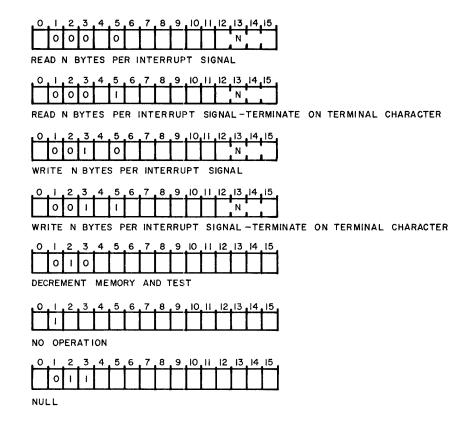

| 2-7         | Bit Configuration For Channel Command Word         | 2-13              |

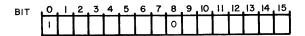

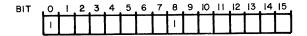

| 2-8         | Channel Command For Initialize and Output Commands | 2-13<br>2-14      |

| 2-9<br>2-10 | Channel Command Words for Termination              | 2-14 $2-15$       |

# **ILLUSTRATIONS**

| Figure       |                                                            | Page         |

|--------------|------------------------------------------------------------|--------------|

| 2-11<br>2-12 | Automatic I/O First/Second Channel Command Block           | 2-16<br>2-18 |

|              |                                                            |              |

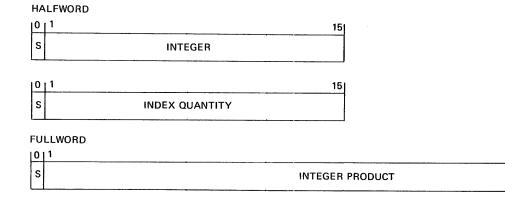

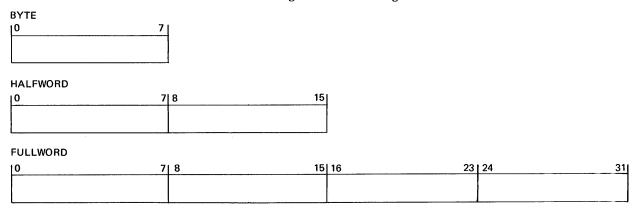

| 3-1          | Fixed-Point Word Formats                                   | 3-2          |

| 3-2          | Floating-Point Word Format                                 | 3-3          |

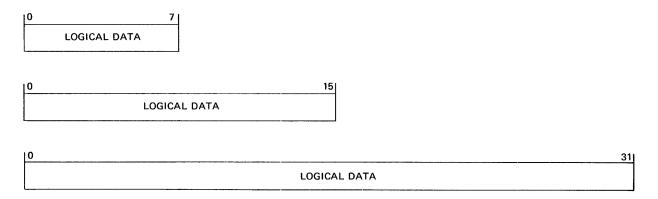

| 3-3          | Logical Data Word Formats                                  | 3-4          |

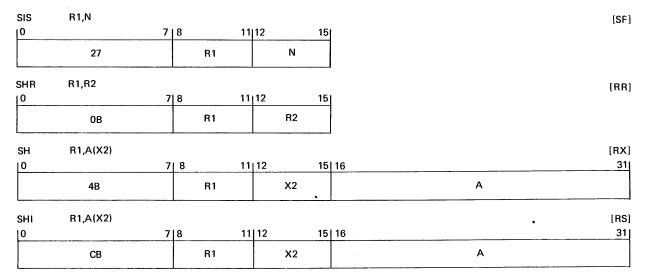

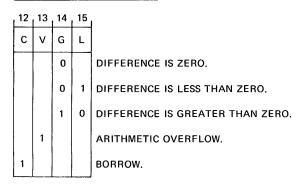

| 3-4          | Instruction Word Formats                                   | 3-5          |

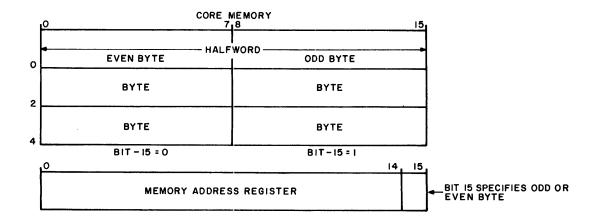

| 3-5          | Data Word Formats                                          | 3-7          |

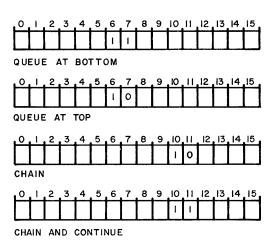

| 4-1          | Circular List                                              | 4-57         |

| 5-1          | Input/Output Rate Comparison                               | 5-1          |

| 5-2          | System Interface, Block Diagram                            | 5-2          |

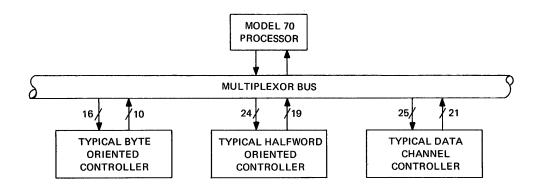

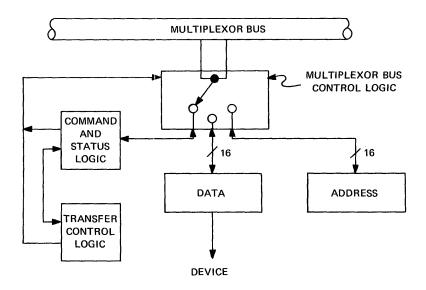

| 5-3          | Multiplexor Channel, Block Diagram                         | 5-3          |

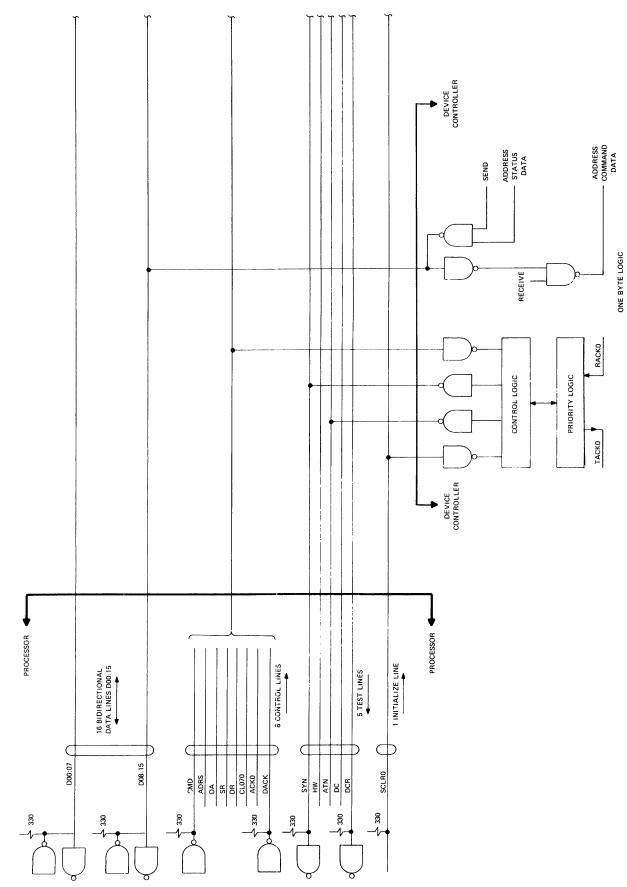

| 5-4          | Processor/Device Controller Logic Interface (Sheet 1 of 2) | 5-6          |

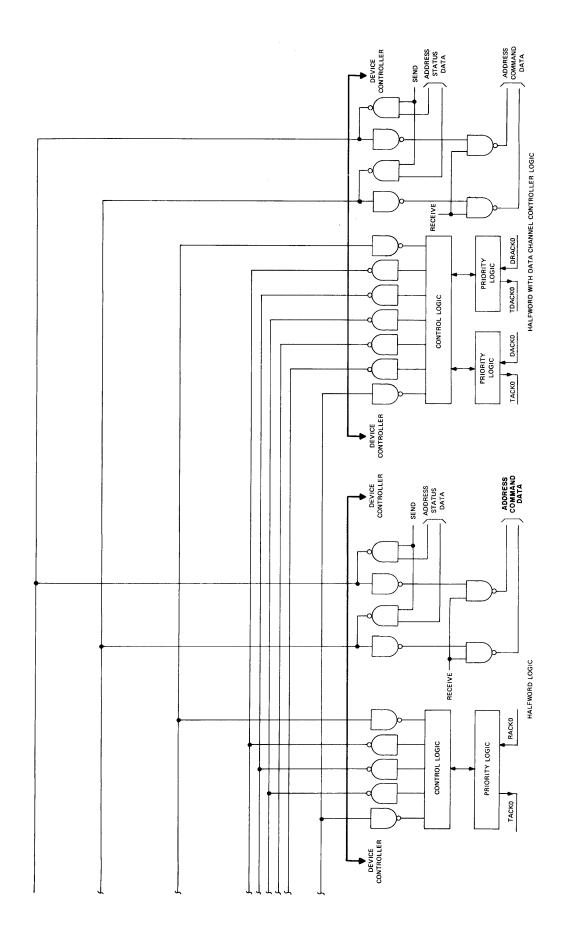

| 5-4          | Processor/Device Controller Logic Interface (Sheet 2 of 2) | 5-7          |

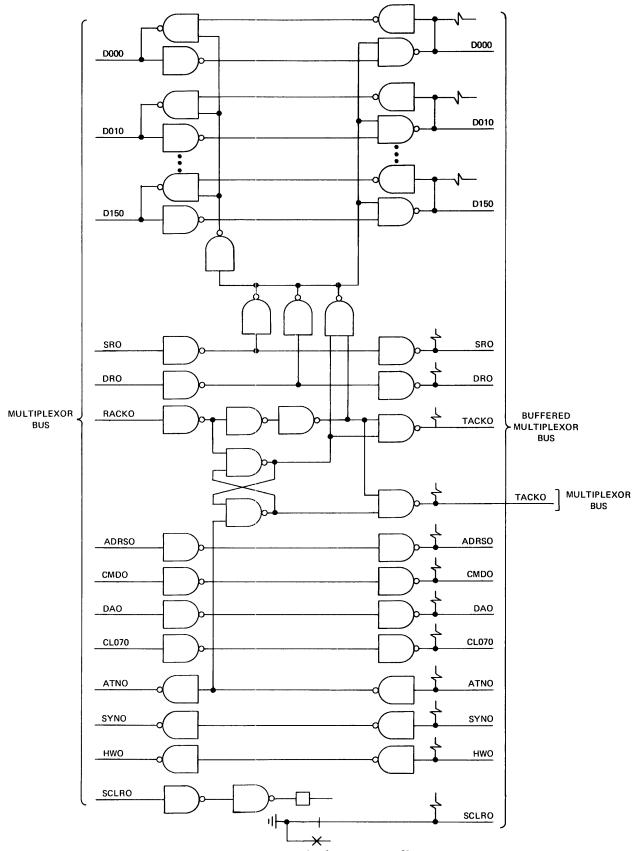

| 5-5          | Multiplexor Bus Buffer                                     | 5-8          |

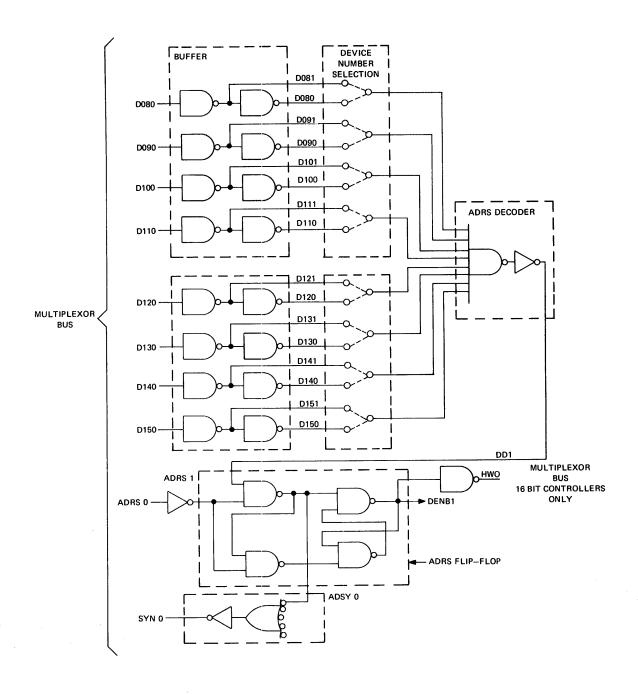

| 5-6          | Device Addressing, Logic Diagram                           | 5-10         |

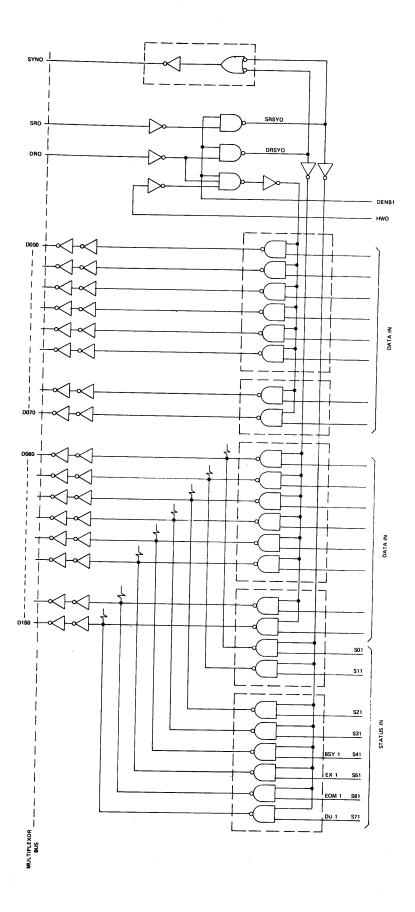

| 5-7          | Data and Status Input Logic Diagram                        | 5-11         |

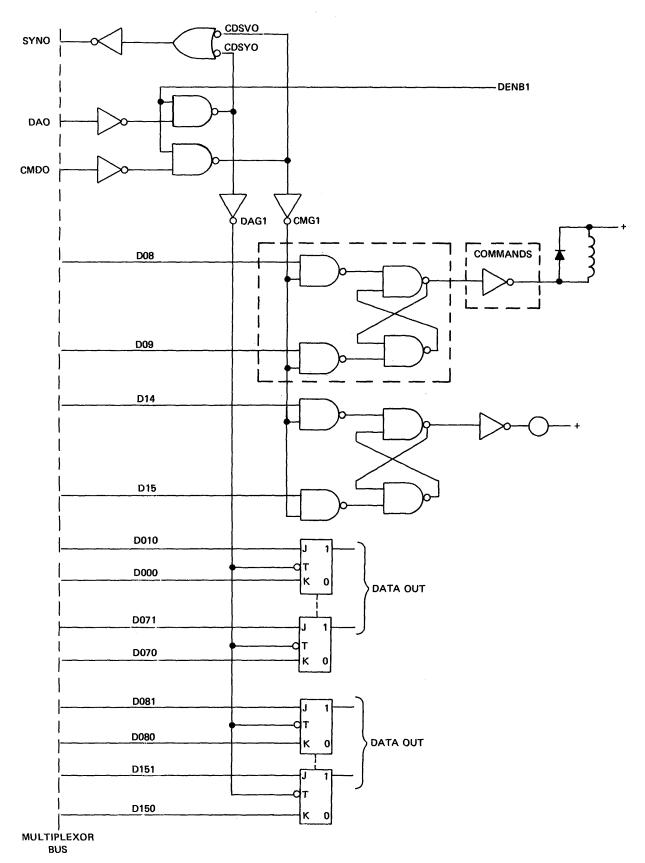

| 5-8          | Data and Command Output, Logic Diagram                     | 5-13         |

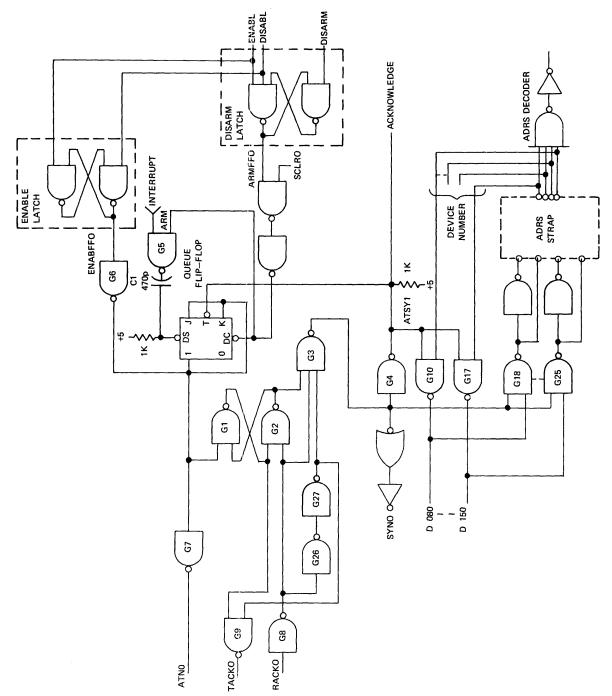

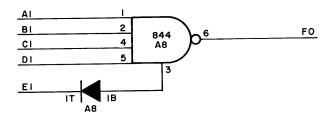

| 5-9          | Interrupt Control, Logic Diagram                           | 5-14         |

| 5-10         | Typical Universal Expansion Slot Wiring                    | 5-16         |

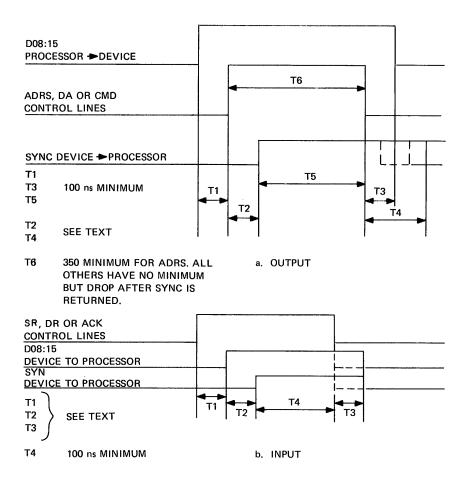

| 5-11         | Multiplexor Channel Timing                                 | 5-17         |

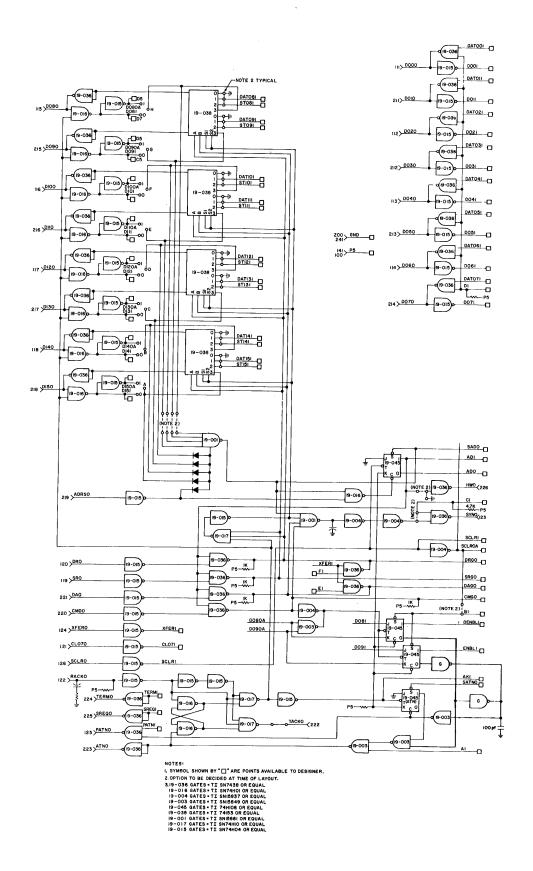

| 5-12         | General Multiplexor Bus Interface                          | 5-19         |

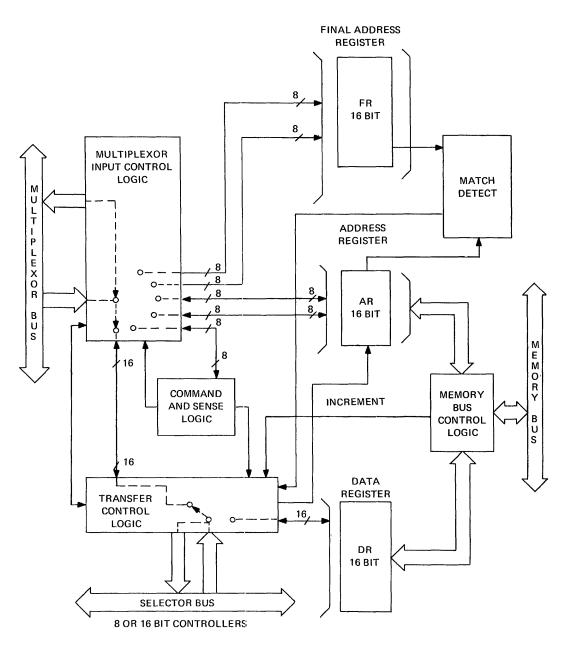

| 5-13         | Interleaved Data Channel, Block Diagram                    | 5-20         |

| 5-14         | Data Channel Timing Chart                                  | 5-21         |

| 5-15         | Data Channel/Multiplexor Bus Interface                     | 5-22         |

| 5-16         | Typical Memory Cycle                                       | 5-23         |

| 5-17         | MOS Memory Cycle                                           | 5-23         |

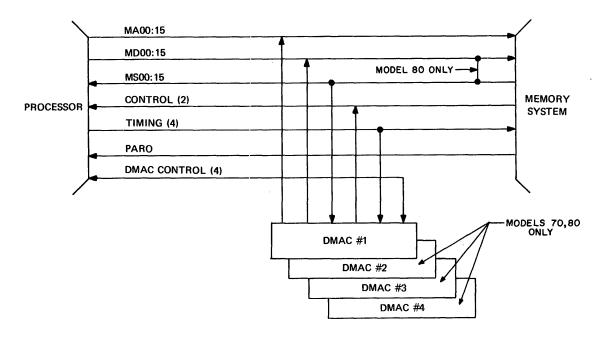

| 5-18         | Memory Bus Diagram                                         | 5-24         |

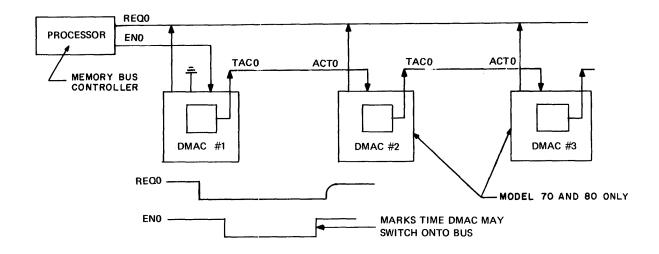

| 5-19         | Example of Memory Bus Priorities                           | 5-24         |

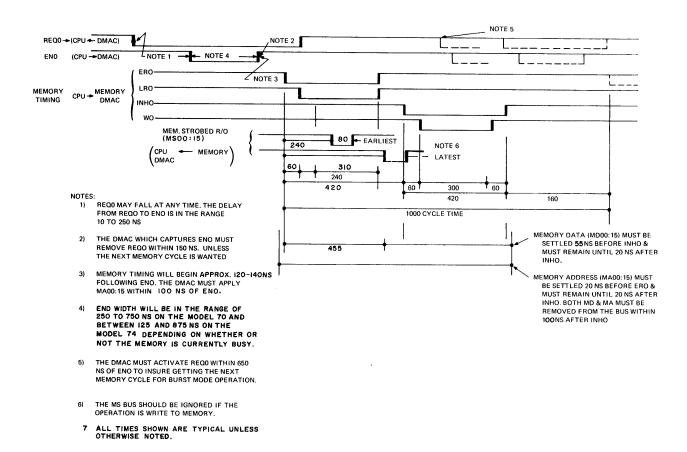

| 5-20         | Model 74 and 70 Memory Bus Timing                          | 5-25         |

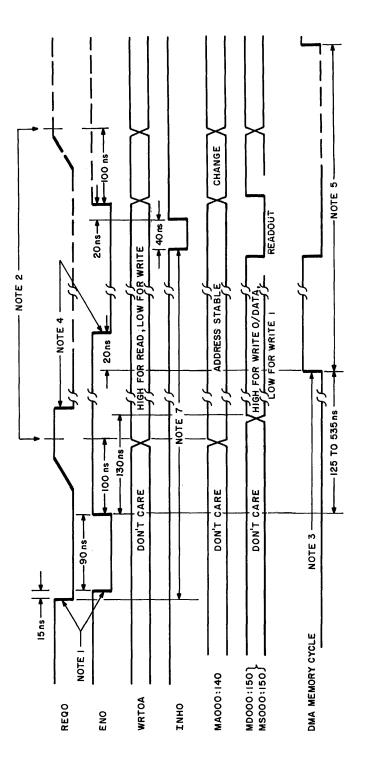

| 5-21         | Model 80 Memory Bus Timing                                 | 5-26         |

| 5-22         | Typical Control Logic for Interfacing to the Memory Bus    | 5-27         |

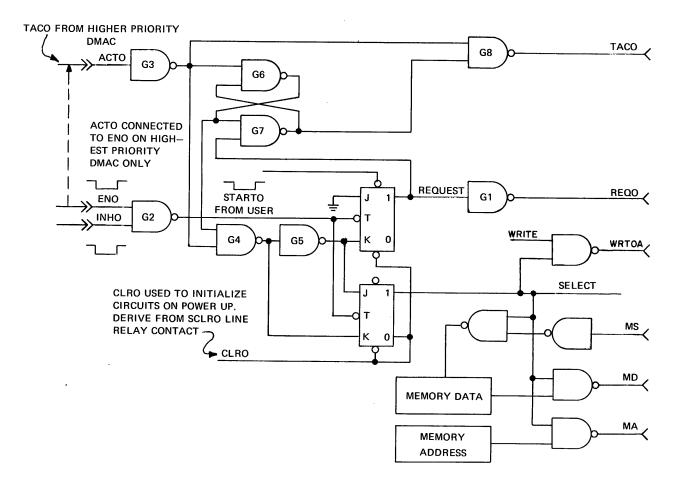

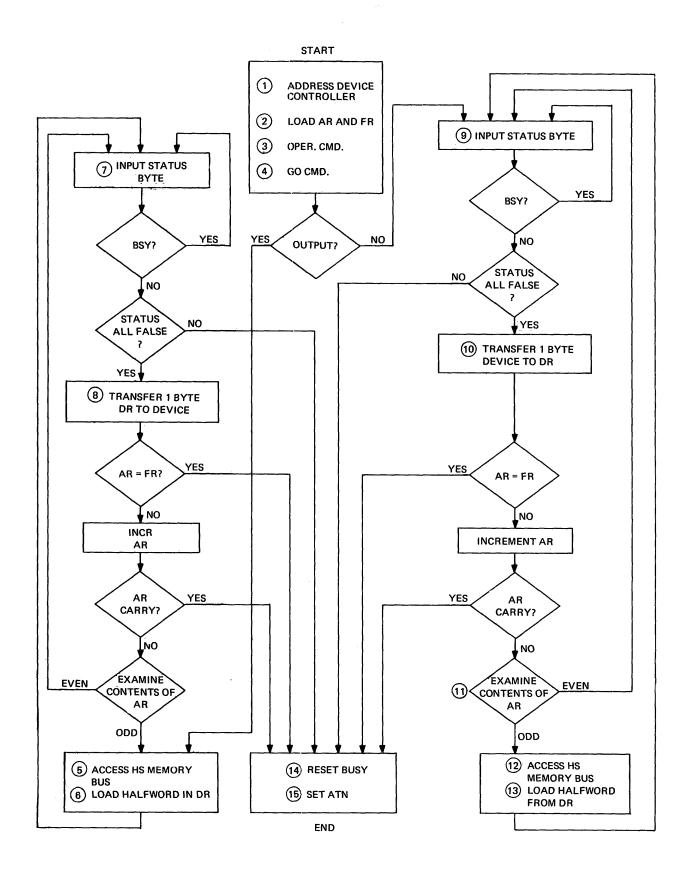

| 5-23         | Selector Channel, Block Diagram                            | 5-30         |

| 5-24         | Selector Channel, Flow Chart                               | 5-32         |

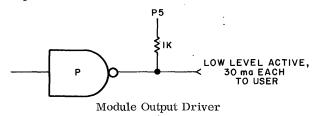

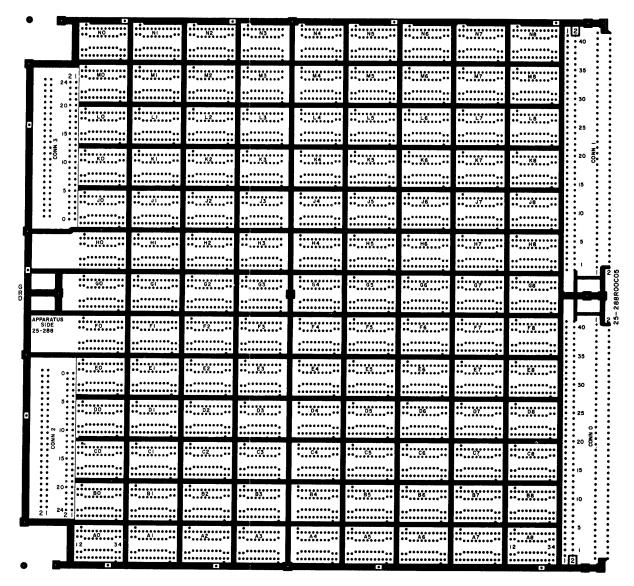

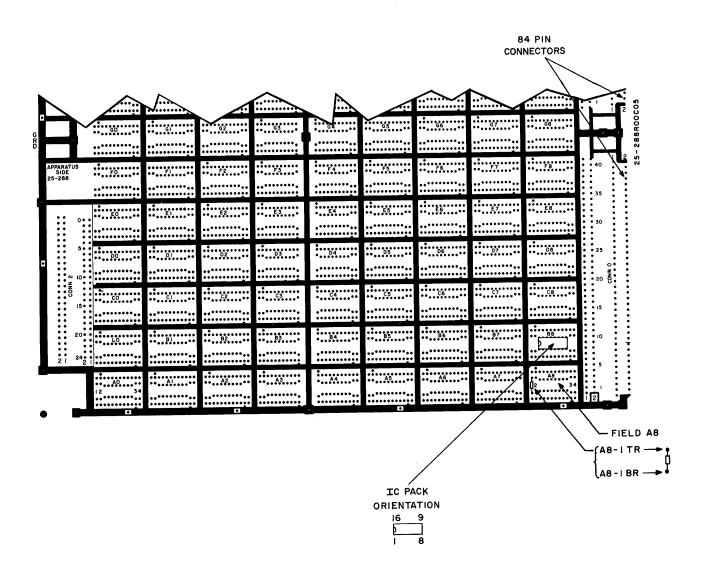

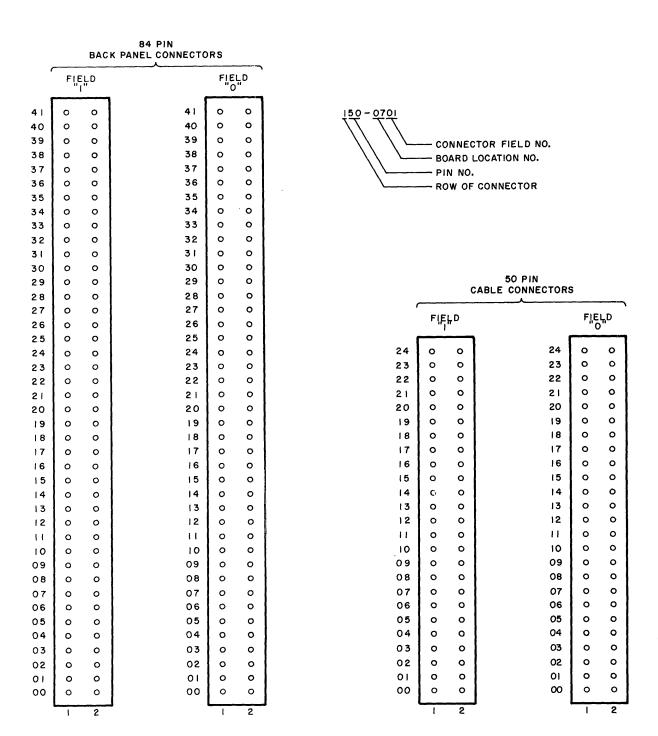

| 5-25         | General Purpose Wire Wrap Board                            | 5-36         |

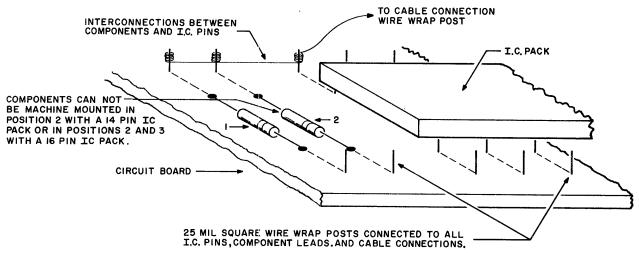

| 5-26         | Wire Wrap Posts/IC and Component Leads Connection          | 5-36         |

| 5-27         | IC Circuit Board Numbering System                          | 5-37         |

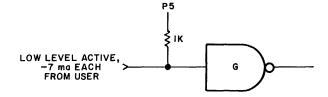

| 5-28         | Example of a Power Gate                                    | 5-37         |

| 5-29         | General Purpose Interface Board Connector Layout           | 5-38         |

| 6-1          | Control Console                                            | 6-2          |

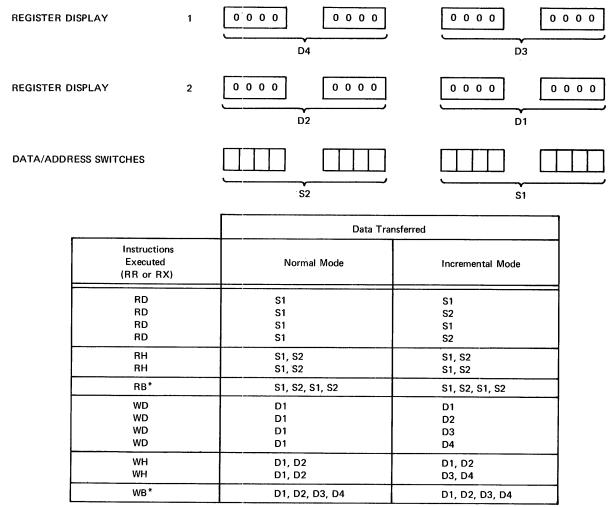

| 6-2          | Control Console Data Transfers                             | 6-8          |

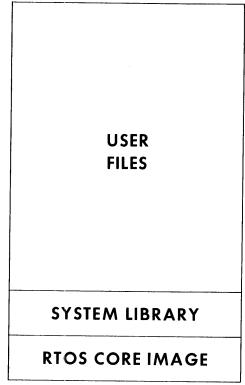

| 7-1          | INTERDATA Software                                         | 7-1          |

| 7-2          | BOSS Features                                              | 7-1          |

| 7-3          | DOS Features                                               | 7-1          |

| 7-4          | RTOS Features                                              | 7-1          |

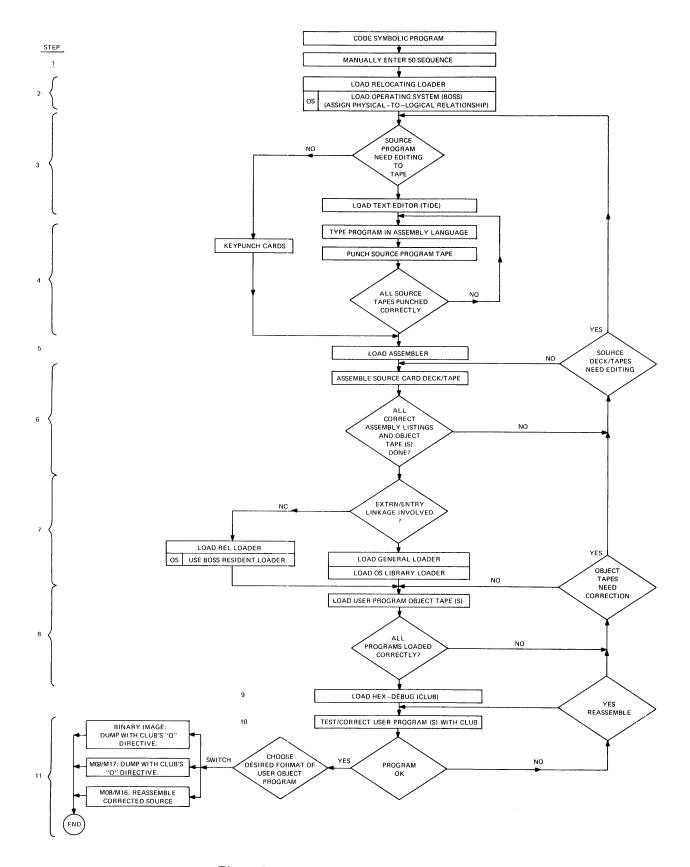

| 7-5          | Program Preparation Sequence                               | 7-4          |

| 7-6          | Conditional Assembly Structures                            | 7-37         |

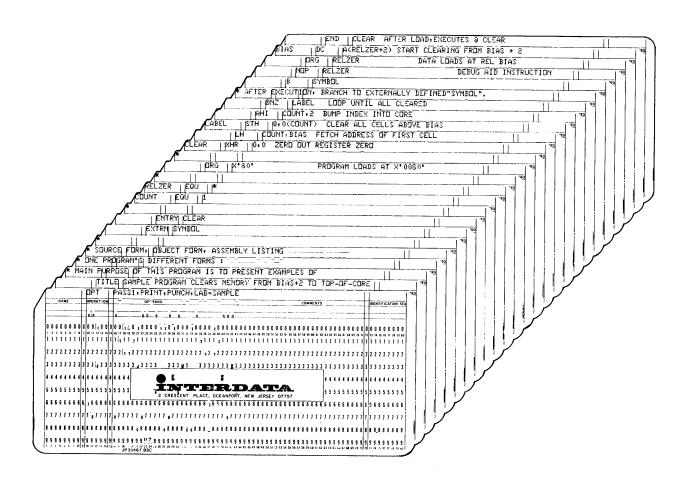

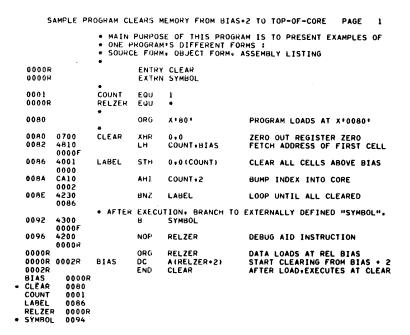

| 7-7          | Sample Program Source Deck                                 | 7-38         |

## **ILLUSTRATIONS**

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

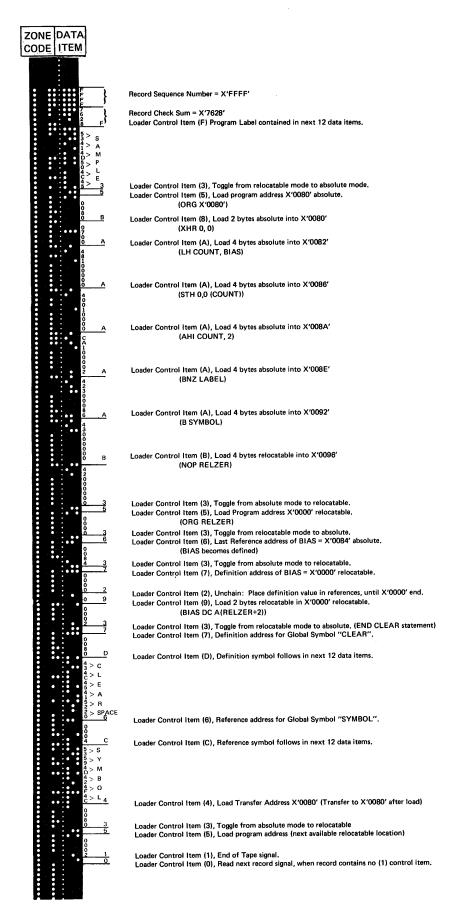

| 7-8    | Sample Program One-Pass Object Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-39   |

| 7-9    | Sample Program One-Pass Assembly Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-40   |

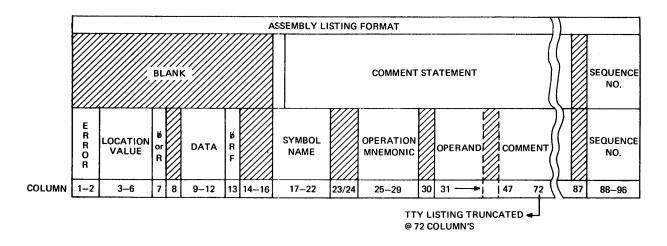

| 7-10   | Assembler Print Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-40   |

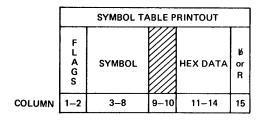

| 7-11   | Basic Assembler Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 - 43 |

| 7-12   | PASS1 Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-48   |

| 7-13   | PASS2 Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-49   |

| 7-14   | PASS3 Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-49   |

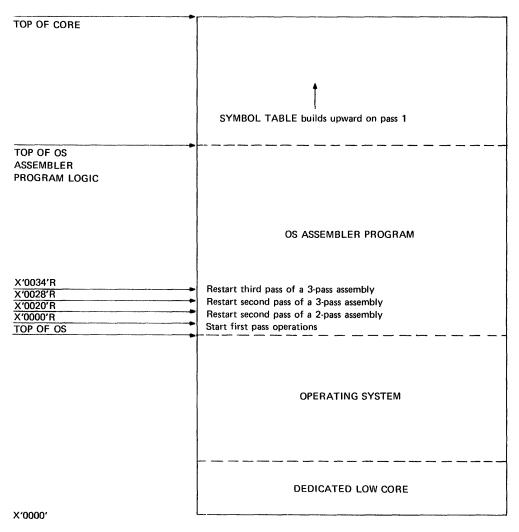

| 7-15   | OS Assembler Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-52   |

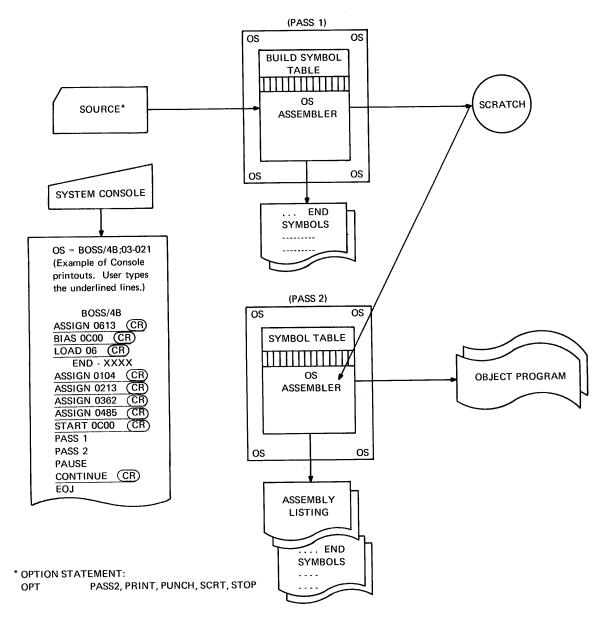

| 7-16   | OS Assembler PASS2 Assembly with Scratch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-59   |

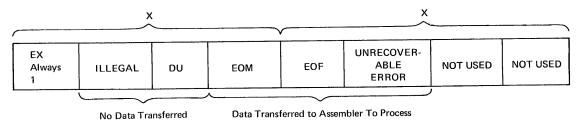

| 7-17   | I/O Error Message Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-59   |

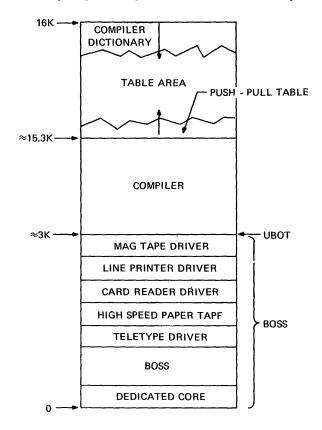

| 7-18   | Memory Map at Compile Time Using BOSS/4B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-67   |

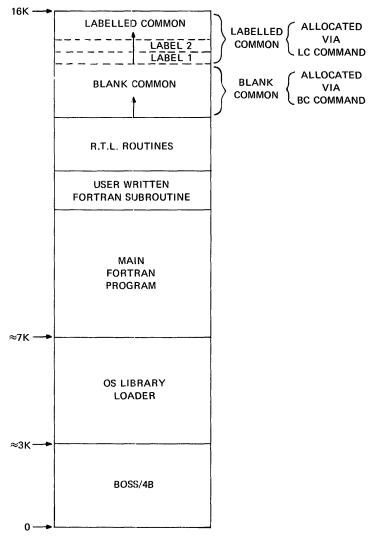

| 7-19   | Execution Time Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-70   |

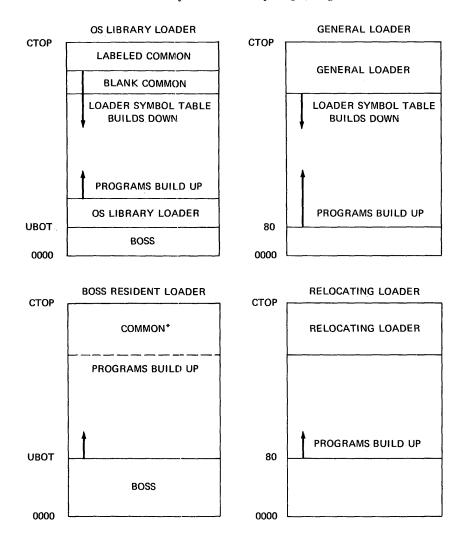

| 7-20   | Loader Memory Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-76   |

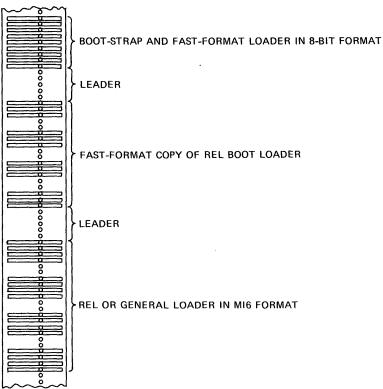

| 7-21   | Loader Tape Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-79   |

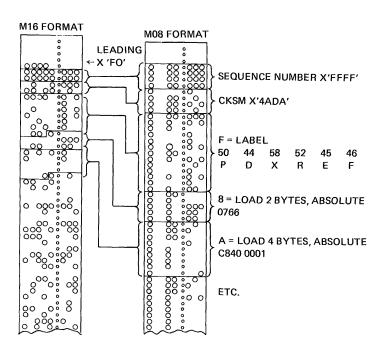

| 7-22   | Object Tape Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-83   |