**Digital Teaching Aid**

# **Table of Contents**

| Digital Teaching Aid                    | 1  |

|-----------------------------------------|----|

| Preface                                 | 1  |

| Introduction                            | 2  |

| Fundamental Logic Operations – Lesson 1 |    |

| Lesson Plan                             |    |

| Handout No. 1.                          |    |

| Worksheet No. 1                         | 9  |

| Introduction Boolean Algebra – Lesson 2 | 11 |

| Lesson Plan                             | 11 |

| Worksheet No. 2                         | 17 |

| Circuit Analysis and Design – Lesson 3  | 18 |

| Lesson Plan                             | 18 |

| Handout No. 2                           | 24 |

| Worksheet No. 3                         | 24 |

| First Evaluation                        | 25 |

| Karnaugh Mapping – Lesson 4             | 26 |

| Lesson Plan                             | 26 |

| Worksheet No. 4                         | 34 |

| Karnaugh Mapping II – Lesson 5          | 36 |

| Lesson Plan                             | 36 |

| Worksheet No. 5                         | 40 |

| <u>Coding – Lesson 6</u>                | 41 |

| Lesson Plan                             | 41 |

| Worksheet No. 6                         | 48 |

| <u>Flip–Flops – Lesson 7</u>            |    |

| Lesson Plan                             |    |

| Worksheet No. 7                         |    |

| Second Evaluation                       |    |

| <u>Counter – Lesson 8</u>               |    |

| Lesson Plan                             |    |

| Worksheet No. 8.                        |    |

| Data Processing Circuits – Lesson 9.    |    |

| Lesson Plan                             |    |

| Handout No. 3.                          |    |

| Worksheet No. 9                         |    |

| Third Evaluation                        |    |

| Answers to Evaluation Problems          | 74 |

## **Digital Teaching Aid**

Lehr– und Lernmittel, Informationen, Beratung

Educational Aids Literature, Consulting

Moyens didactiques, Informations, Service–conseil

Material didáctico, Informaciones, Asesoría

GTZ

## Deutsche Gesellschaft für Technische Zusammenarbeit (GTZ) GmbH

Andreas Lange

**Digital Teaching Aid**

91-34-0308/2

Andreas Lange, DED, 1994 Philippines

## Preface

Nearly two years ago the German Development Service (DED) offered me the possibility to assist a technical college in the Philippines.

I had finished my studies in electronic engineering in Germany and had gained several years of working experience in the development of medical electronic equipment and the organization of telecommunication units.

Since I have been assigned with the Don Bosco Technical College, I have been teaching in electronics, computer science, and have been working in the training for instructors.

One of the mayor problems I encountered was the lack of preparation time for the lessons. Many teachers are under steady time pressure because they have to serve two or more jobs in order to earn the adequate income. That gave me the idea to develop a ready-made lesson preparation for teachers.

Based on my experience and also due to the visit of many other schools I edited and compiled this Teaching Aid. I tried to integrate practice and theory which is the best way to provide a solid foundation. I hope this will support the teachers as well as it can improve the quality of classes.

Canlubang, Philippines February 1994

Andreas Lange

## Introduction

This Teaching Aid is addressed to teachers and schools which offer any kind of electronic courses (i.e. computer maintenance, machine control, radio and tv repair, etc). It provides the basic knowledge for technicians as well as it can be used to run basic courses at technical colleges.

Digital Teaching Aid is a teaching module made for teachers. It is a ready – made lesson preparation and not a textbook. Therefore, you (the teacher) should already have some background knowledge on digital electronics. This module gives you all the material you need to run a course in basic digital electronics.

The module is divided into lessons, each lesson is headed by a lesson plan followed by boardscripts, worksheets, and handouts. It also contains three evaluations which you can use as tests/exams or as advanced exercises. The lesson plans are not only containing the contents of the lesson, but also gives you the objectives and suggested methods and ways to carry out the lesson. The following informs you about the purpose of every lesson plan column:

| Time   | <ul> <li>The 'Time' column is still blank, it is up to you to decide how much time you would like<br/>to spend on each topic. The average time per lesson is approximately 90 minutes and<br/>45 minutes for the review exercise (Worksheet).</li> </ul>                                                                                            |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Method | – The 'Method' column suggests a sample of teaching methods. Lesson plan 1 and 2 are already filled up to give you an example on how to use this column. I recommend the use of abbreviations, the meaning of every abbreviation is given at the bottom of every method column.                                                                     |

| Торіс  | – The 'Topic' column gives you a brief description of the contents of every lesson. Feel<br>free to add or drop some topics. Every topic is handled in the following boardscript<br>pages.                                                                                                                                                          |

| Way    | – The 'Way' column suggests a sample of teaching tools. Lesson plan 1 and 2 are already filled up. The explanation for the abbreviation used is given at the bottom of every way column. The boardscript pages of every lesson contain examples (EX) and hands on (HO) exercises. The HO's should be carried out by the students during the lesson. |

| Remark | – The 'Remark' column provides you with space for additional information. (i.e.: Where can I find the transparency/picture which I decided to use, or: What is the filename of the demo program which I already prepared)                                                                                                                           |

## Lesson Plan

Titel: Fundamental Logic Operations

Objectives:

## – Understand the principle of NOT, AND, OR operations

– Able to convert binary and decimal numbers

| Time | Method                                                               | Торіс                                              | Way                                                                                                | Remark                                |

|------|----------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|

|      | S,D                                                                  | * Introduction                                     | Ex                                                                                                 |                                       |

|      |                                                                      | <ul> <li>Analog and digital<br/>signals</li> </ul> |                                                                                                    |                                       |

|      | S,Q/A                                                                | * Review                                           | В                                                                                                  |                                       |

|      |                                                                      | -Transistor in hard saturation                     |                                                                                                    |                                       |

|      |                                                                      | <ul> <li>Inverter function</li> </ul>              |                                                                                                    |                                       |

|      | S,D                                                                  | *TTL circuits                                      | В                                                                                                  |                                       |

|      |                                                                      | -History                                           |                                                                                                    |                                       |

|      |                                                                      | - Standards                                        |                                                                                                    |                                       |

|      | S                                                                    | * Logic operations                                 | В                                                                                                  |                                       |

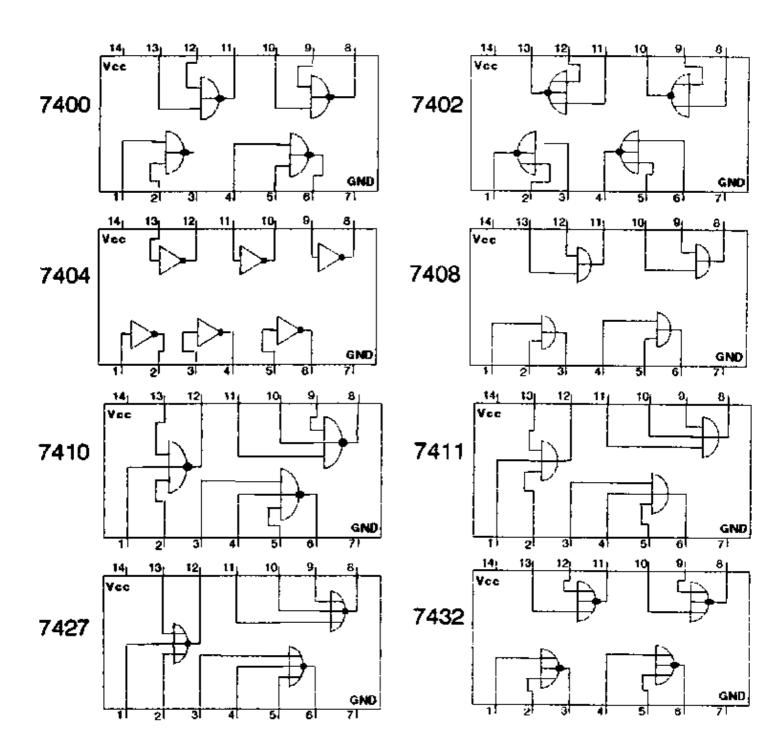

|      | S,E                                                                  | -NOT                                               | НО                                                                                                 | Handout No. 1 (Family of TTL devices) |

|      | S,E                                                                  | -AND                                               | EX                                                                                                 |                                       |

|      | S,E                                                                  | –OR                                                | EX                                                                                                 |                                       |

|      | E                                                                    | * Binary number system                             | WS                                                                                                 | Worksheet No. 1                       |

|      | S: Speech<br>D: Discussion<br>Q/A:<br>Question/Answer<br>E: Exercise |                                                    | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO:<br>Hands-On<br>WS:<br>Worksheet<br>HT: Hand-Out |                                       |

#### Introduction

Fundamental Logic Operations

## **Digital Electronics**

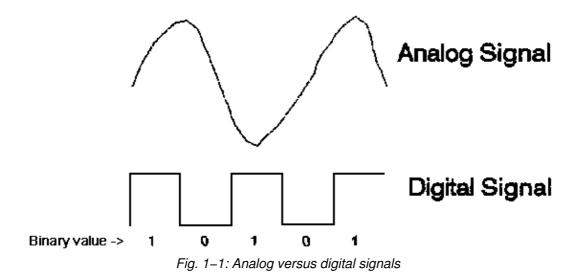

The world of electronics is divided into two areas: analog and digital. Analog circuits consist mainly of amplifiers for voltage or current variations that are smooth and continuous. Digital circuits provide electronic switching of voltage pulses. A pulse has abrupt changes between two extreme amplitude levels (i.e.: 5 volt = high level and 0 volt = low level).

Since the digital signal has only two significant levels, either high or low, it is useful to represent the pulses in a binary number system with the digits 1 and 0. (see also Worksheet 1, Binary number system)

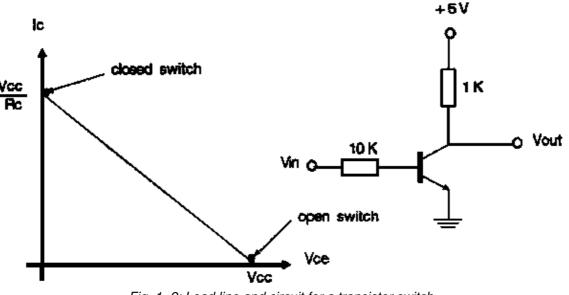

Transistor in digital electronic

A transistor can be used in analog and digital electronic. In digital electronic the transistor operates usually in hard saturation. (see also Amplifier Teaching Aid, Transistor as switch)

Fig. 1–2: Load line and circuit for a transistor switch

Hard Saturation

To get hard saturation, a designer makes  $I_{\rm C}$  approximately 10 times the value of  $I_{\rm B}$ .

When the max. Vin equals to the supply voltage you can get hard saturation by using a ratio of:

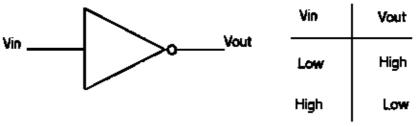

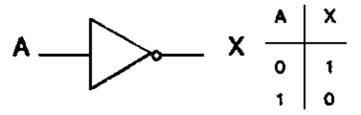

Inverter Function

A transistor switch (circuit as above) can be used to build the first device in digital electronic, the inverter:

Fig. 1–3: Inverter symbol and truth table

Because in digital electronics mainly ready made devices are used (Integrated circuits IC), we don't care any more how the single device is built up. From now on we will use only these ready made devices.

#### **TTL circuits**

1964 TEXAS Instruments introduced a family of digital devices which became standard elements in digital electronic: The TTL (Transistor Transistor Logic) circuits. The High (1) and Low (1) state is represented by voltage levels.

#### Logic operations

All decisions and operations can be realized by means of the three basic operations:

NOT, AND, OR

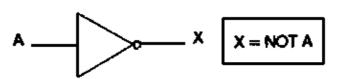

## NOT (Inverter)

Fig. 1–5: NOT (Inverter) symbol and truth table

Circuit example: 7404 TTL device (see Handout No. 1)

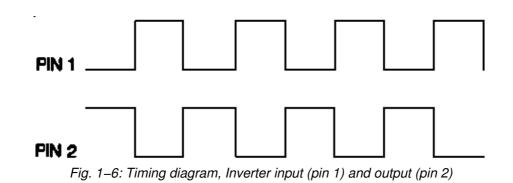

HO: A 1KHz square wave drives pin 1 of a 7404. What does the voltage waveform at pin 2 look like?

Solution:

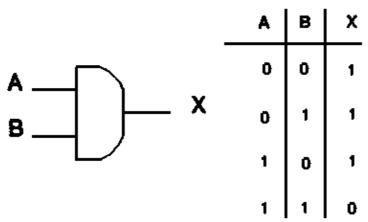

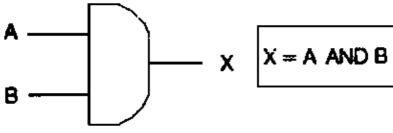

## AND gates

AND operation: The output supplies an high (1) signal if to all inputs high (1) signals are applied.

Fig. 1-6: AND symbol and truth table

AND application example: An elevator motor may only start to work if the doors are shut AND an operation occured.

Circuit example: TTL device 7408, two input AND gate

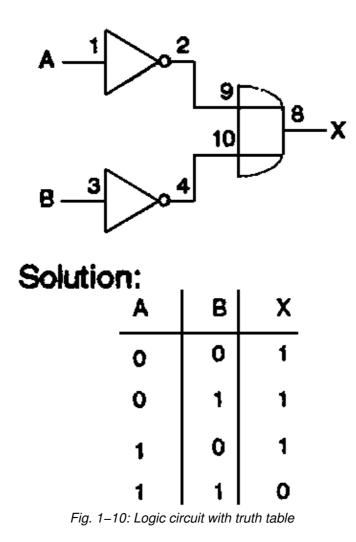

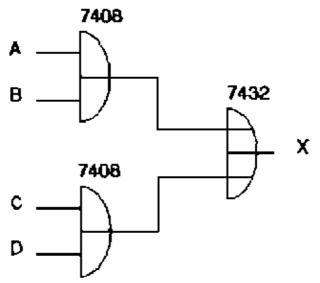

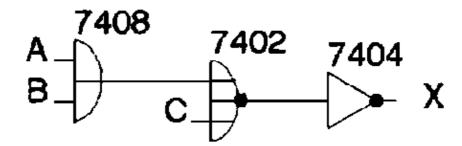

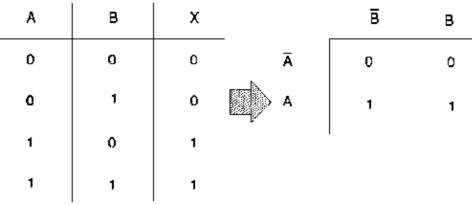

Ex: Develop the truth table for the following logic circuit.

Fig. 1-8: Logic circuit with truth table

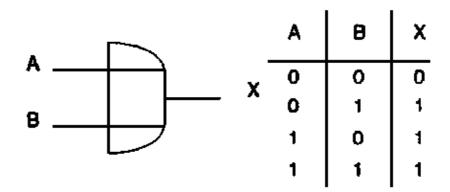

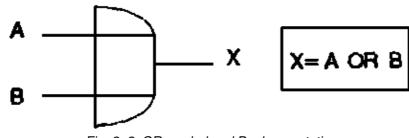

OR gates

OR operation: An OR operation supplies a high signal at the output if to one or more inputs high signals are applied.

Fig. 1–9: OR gate, symbol and truth table

<u>OR application example:</u> A pump has to be switched on when the water level has fallen to a certain level OR too much water is taken out of the container.

Circuit example: TTL device 7432, two input OR gate

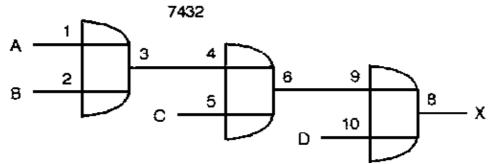

Ex: Develop the truth table for the following logic circuit.

## Handout No. 1

The 7400 Family of TTL Devices (Sample List)

| Device number | Description               |

|---------------|---------------------------|

| 7400          | Quad 2 input NAND gates   |

| 7402          | Quad 2 input NOR gates    |

| 7404          | Hex inverter              |

| 7408          | Quad 2 input AND<br>gates |

| 7410          | Triple 3 input NAND gates |

| 7411          | Triple 3 input AND gates  |

| 7427          | Triple 3 input NOR gates  |

| 7432          | Quad 2 input OR<br>gates  |

Worksheet No. 1

Binary number system

All number systems have a base, which specifies how many digits can be used in each place count. For binary numbers the base is 2, with 0 and 1 as the only two digits. In the decimal system, the base is 10.

Decimal digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9

Binary digits: 0, 1

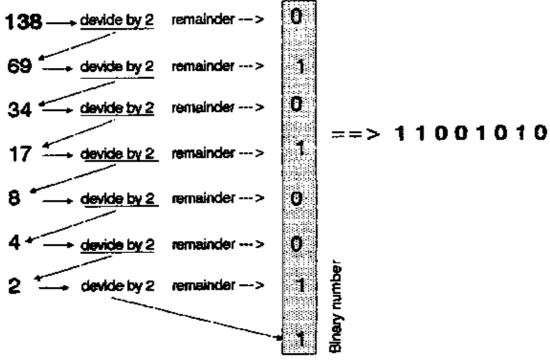

**Decimal to Binary Conversion**

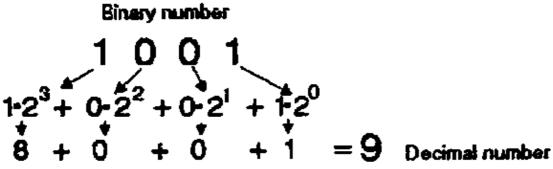

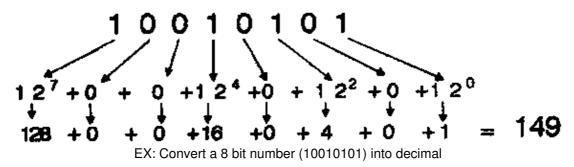

EX: Convert a 4 bit binary number (100 1) into decimal.

Each digit position has specified weight, for binary numbers the position represents a power of two.

HO: Convert the following binary numbers into decimal:

101, 1100, 1110, 1000, 0110, 11001010, 01101111, 10001100

Binary to decimal conversion

EX: Convert the decimal number 138 into a binary number

HO: Convert the following decimal numbers into binary numbers:

12, 8, 127, 247, 139, 255

## Lesson Plan

### Introduction

Titel: Introduction Boolean Algebra

Objectives:

- Able to express the basic operations in Boolean algebra

- Know how to describe a logic circuit in a Boolean equation

- Understand the basic Boolean theorems.

| Time |                                                                           | Method |   | Торіс                                     | Way                                                                                          | Remark          |

|------|---------------------------------------------------------------------------|--------|---|-------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|

|      | Q/A                                                                       |        | * | Review Lesson 1                           | В                                                                                            |                 |

|      | s                                                                         |        | * | Introduction – George Boole               | В                                                                                            |                 |

|      | s                                                                         |        | * | Boolean algebra                           | B,Ex                                                                                         |                 |

|      |                                                                           | S,E    |   | - NOT operation                           |                                                                                              |                 |

|      |                                                                           |        |   | - OR operation                            |                                                                                              |                 |

|      |                                                                           |        |   | - AND operation                           |                                                                                              |                 |

|      |                                                                           | S,E    |   | - Boolean equations of logic circuits     | B,Ex                                                                                         |                 |

|      |                                                                           |        |   | <ul> <li>NOR gates Truth table</li> </ul> | В                                                                                            |                 |

|      |                                                                           | S,D    |   | – De Morgan's 1. theorem                  | В                                                                                            |                 |

|      |                                                                           |        |   | - NAND gates Truth table                  | В                                                                                            |                 |

|      |                                                                           | E      |   | – De Morgan's 2. theorem                  | B,HO                                                                                         |                 |

|      | E * Re                                                                    |        | * | Review Exercise                           | WS                                                                                           | Worksheet No. 2 |

|      | E<br>S: Speech<br>D: Discussion<br>Q/A:<br>Question/Answer<br>E: Exercise |        |   |                                           | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO: Hands–On<br>WS: Worksheet<br>HT: Hand–Out |                 |

#### Boolean algebra

George Boole (1854) invented a new kind of algebra that could be used to analyse and design digital and computer circuits.

NOT operation

Fig. 2–1: Inverter symbol and Boolean notation

Ex: If A is 0 (low) ? X = NOT 0 = 1

In Boolean algebra the overbar stands for NOT operation.

$$X = \overline{A}$$

OR operation

Fig. 2–2: OR symbol and Boolean notation

Ex: If A = 0, B = 1 ? X = A or B = 0 or 1 = I

In Boolean algebra the + sign stans for the OR operation:

$\mathsf{X}=\mathsf{A}+\mathsf{B}$

<u>Ex:</u> If A = 1, B = 0 ? X = A + B = 1 + 0 = 1

AND operation

Fig. 2-3: AND symbol and Boolean notation

In Boolean algebra the multiplication sign stands for the AND operation:

$\mathsf{X}=\mathsf{A}\bullet\mathsf{B}$

or simply:

X = A B

<u>Ex:</u> If A = 1, B = 0?  $X = A B = 1 \cdot 0 = 0$

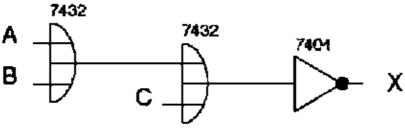

#### Boolean equations of logic circuits

You can use Boolean algebra as a shorthand notation for digital circuits.

Fig. 2–4: Digital circuit

Output of the first gate:

X3 = A + B

Output of the second gate:

$$X6 = X3 + C = A + B + C$$

The final output is:

X8 = X6 + D = A + B + C + D = X

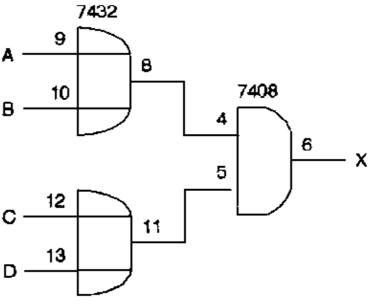

HO: Find the Boolean equation for the following circuit.

Fig. 2–5: Logic circuit

Solution:

X = (A + B) (C + D)

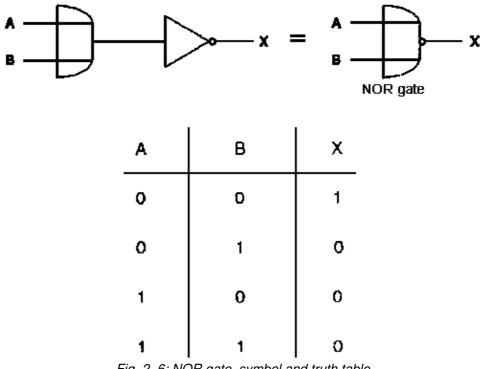

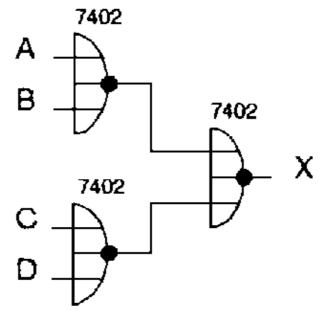

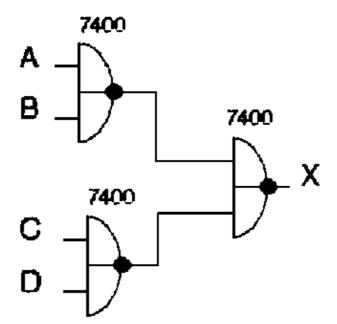

### NOR and NAN gates

## NOR gate

Based on the three fundamental logic operations it is possible to design additionel logic devices.

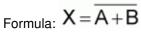

NAND gate

Formula:  $X = \overline{A B}$

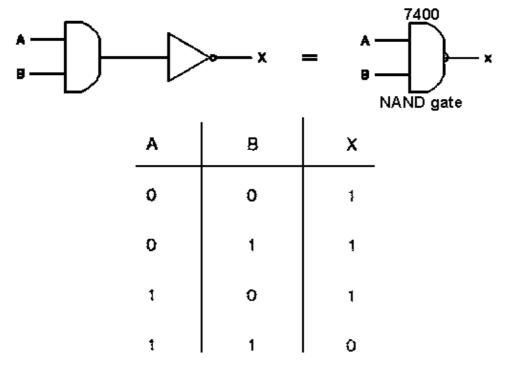

#### De Morgan's theorems

Augustus De Morgan was the first who found the link between logic and mathematics.

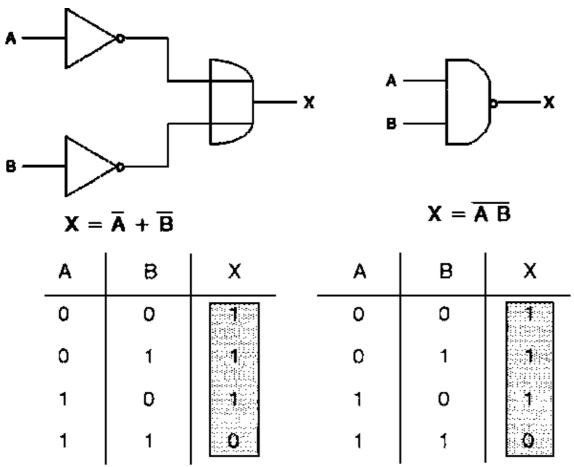

Fig. 2–8: Logic circuits with the same output

Although the circuits are different but the output, as we can see in the truth table, is equal. Therefore we can write:

$\overline{A}\overline{B} = \overline{A+B}$

### De Morgan's First Theorem

Also if we compare the two circuits on the next page we can easily see that the output is the same, although the circuits are different.

(see Fig. 2-9)

Fig. 2–9: Logic circuits with the same output

So we can write:

$$\overline{AB} = \overline{A} + \overline{B}$$

De Morgan's Second Theorem

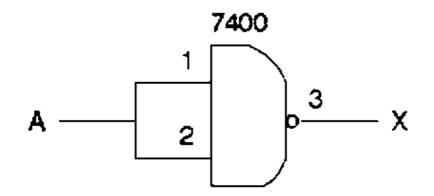

HO: How can you connect a NAND gate to get an inverter

Solution:

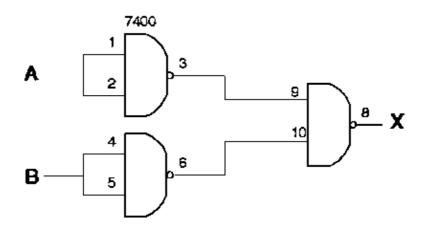

HO: How can you connect NAND gates to get an OR gate?

## Solution:

Worksheet No. 2

No. 1 What is the Boolean equation? What is the truth table?

No. 2 What is the Boolean equation? What is the truth table?

No. 3 What is the Boolean equation? What is the truth table?

No. 4 Construct the truth table.

No. 5 Draw the logic circuit whose Boolean equation is

$$X = \overline{A + B} + \overline{C}$$

Use the 7404 and the 7432 with pin numbers

No. 6 Draw the logic circuit whose Boolean equation is

## $X = \overline{ABC} + A\overline{BC}$

Use the 7404, 7432 and the 7411 with pin numbers.

## **Circuit Analysis and Design – Lesson 3**

## Lesson Plan

Titel: Circuit Analysis and Design

Objectives:

- Know how to apply the basic Boolean laws

- Able to create digital circuits with the help of the sum of products method

| Time         Method         Topic         Way         Remark |  |

|--------------------------------------------------------------|--|

|--------------------------------------------------------------|--|

|                                                                     | * | Review Lesson 2                                                     |                                                                                                       |                                             |

|---------------------------------------------------------------------|---|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------|

|                                                                     | * | Introduction                                                        |                                                                                                       |                                             |

|                                                                     | * | Boolean laws and theorems                                           | НО                                                                                                    | Handout No. 2 (Boolean<br>Algebra Theorems) |

|                                                                     |   | - Basic laws                                                        |                                                                                                       |                                             |

|                                                                     |   | <ul> <li>Boolean relation about OR operations</li> </ul>            |                                                                                                       |                                             |

|                                                                     |   | <ul> <li>Boolean relations about</li> <li>AND operations</li> </ul> |                                                                                                       |                                             |

|                                                                     | * | Sum of products method                                              |                                                                                                       |                                             |

|                                                                     |   | <ul> <li>Fundamental products</li> </ul>                            |                                                                                                       |                                             |

|                                                                     |   | - Sum of products equations                                         |                                                                                                       |                                             |

|                                                                     | * | Review Exercise                                                     | WS                                                                                                    | Worksheet No. 3                             |

| S: Speech<br>D: Discussion<br>QA:<br>Question/Answer<br>E: Exercise |   |                                                                     | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO:<br>Hands-On<br>WS:<br>Worksheet<br>HT:<br>Hand-Out |                                             |

#### Introduction

Circuit Analysis and Design

#### Boolean laws and theorems

Basic laws

(see also Handout No. 2)

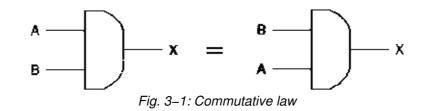

Commutative law:

$$A + B = B + A$$

A B = B A

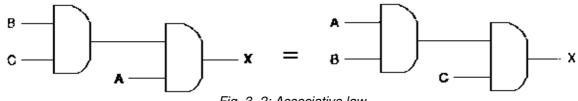

Associative law:

$$A + (B + C) = (A + B) + C$$

$A (B + C) = (A B) C$

Fig. 3–2: Associative law

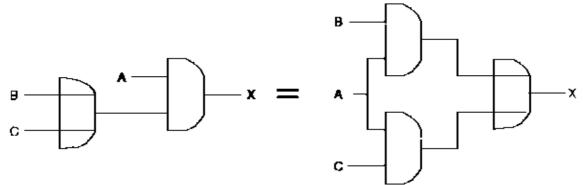

Distributive law:

$$A (B + C) = AB + AC$$

Boolean relations about OR operations

$\mathsf{A} + \mathsf{0} = \mathsf{A}$

Proof:

when A is 0

0 + 0 = 0

when A is 1

1 + 0 = 1

$\mathsf{A} + \mathsf{A} = \mathsf{A}$

## Proof:

when A is 0

0 + 0 = 0

when A is 1

1 + 1 = 1

A + 1 = 1

## Proof:

when A is 0

0 + 1 = 1

when A is 1

1 + 1 = 1

$\mathsf{A} + \mathsf{A} = 1$

If one input is high, the output is high no matter what the other input is.

Boolean relations about AND operations

HO: Check the equations above in the same way as we did it before.

$\mathsf{A} \bullet \mathsf{A} = \mathsf{0}$

If one input is low, the output is low no matter what the other input is.

Double inversion

$\overline{\overline{A}} = B$

De Morgan's theorems

$$\overline{A+B} = \overline{A}\overline{B}_{see \ also \ Lesson \ 1}$$

$\overline{A+B} = \overline{A}B$

Duality theorem

- 1. Change each OR sign to an AND sign

- 2. Change ech AND sign to an OR sign

3. Complement any 0 or 1 appearing in the expression

Ex:

$$A + 0 = A$$

Ex: A(B + C) = AB + AC

? A + B C = (A + B) (A + C)TIP: Proof it with a truth table

Ex: Simplify the following Boolean equation

# $X = A\overline{B} + AB$

Solution: (see also Handout No. 2)

$X = A(\overline{B} + B)$ Handout 2No. 3aX = A(1)No. 8aX = ANo. 7bHO: Simplify the following Boolean equation

$$X = (\overline{A} + B)(A + B)$$

Solution:

$X = \overline{A}A + \overline{A}B + BA + BB$  $X = \overline{A}B + BA + B$  $X = (\overline{A} + A)B + B$ X = B + BX = B

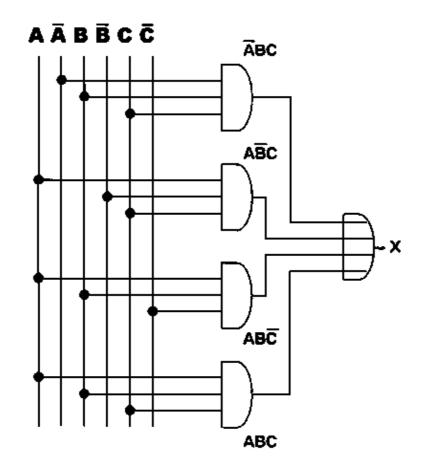

### Sum of product method

Fig. 3-4: Example truth table with fundamental products

| Α | в | x | Fundamental Products |

|---|---|---|----------------------|

| 0 | 0 | 0 | ĀĒĊ                  |

| 0 | 0 | 1 | ĀĒC                  |

| 0 | 1 | 0 | ĀBĒ                  |

| 0 | 1 | 1 | ĀBC                  |

| 1 | 0 | 0 | ABC                  |

| 1 | 0 | 1 | ABC                  |

| 1 | 1 | 0 | ABC                  |

| 1 | 1 | 1 | ABC                  |

## Design example

Sum of products equation

Given is the following truth table:

Fig. 3–5: Example truth table

| Α | в | С | Х |  |

|---|---|---|---|--|

| 0 | 0 | 0 | 0 |  |

| 0 | 0 | 1 | 0 |  |

| 0 | 1 | 0 | 0 |  |

| 0 | 1 | 1 | 1 | ? | ĀBC              |

|---|---|---|---|---|------------------|

| 1 | 0 | 0 | 0 |   |                  |

| 1 | 0 | 1 | 1 | ? | ABC              |

| 1 | 1 | 0 | 1 | ? | $AB\overline{C}$ |

| 1 | 1 | 1 | 1 | ? | ABC              |

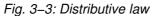

We have to locate each output 1 in the truth table and write down the fundamental product.

The next step is to OR the fundamental products:

$X = \overline{A}BC + A\overline{B}C + A\overline{B}\overline{C} + AB\overline{C}$

Now we can derive the corresponding logic circuit:

HO: What is the sum of product circuit for the given truth table?

Fig. 3–7: Truth table

| Α | в | С | X |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Handout No. 2

## **Boolean Algebra Theorems**

| No         | Theorem                                                   | Name             |

|------------|-----------------------------------------------------------|------------------|

| 1a<br>1b   | A + B = B + A<br>AB = BA                                  | Commutative law  |

| 2a<br>2b   | (A + B) + C = A + (B + C)<br>(AB) C = A (B + C)           | Associative law  |

| 3a<br>3b   | A (B + C) = AB + AC<br>A + (BC) = (A+ B) (A+ C)           | Distributive law |

| 4a<br>4b   | A + A = A<br>AA = A                                       | Identity law     |

| 5a<br>5b   | $\overline{A} = \overline{A}$<br>$\overline{A} = A$       | Negation         |

| 6a<br>6b   | A + AB = A<br>A (A + B) = A                               | Redundancy       |

|            | 0 + A = A<br>1 A = A<br>1 + A = 1<br>0A = 0               |                  |

| 8A<br>8b   | $\overline{A} + A = 1$<br>$\overline{A} A = 0$            |                  |

| 9a<br>9c   | $A + \overline{AB} = A + B$<br>$A(\overline{A} + B) = AB$ |                  |

| 10a<br>10b | $\overline{\frac{A+B}{AB}} = \overline{A}\overline{B}$    | De Morgan's laws |

## Worksheet No. 3

No. 1 Simplify the Boolean equation and discribe the logic circuit:

$\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} = X$

No. 2 Simplify the following Boolean expressions:

$$\overline{A}\overline{B} + AB + \overline{A}B$$

(A + B)(A +  $\overline{B}$ )

$\overline{A}B + A\overline{B} + AB + \overline{A}\overline{B}$

No. 3 A digital system has a 4-bit input from 0000 to 1111. Design a logic circuit that produces a high output whenever the equivalent decimal input is greater than 13.

<u>No. 4</u> In a heating plant the burner X has to be switched on, when the circulating pump A is actuated and the temperature probe B for the warm water supply or the room temperature probe C respond.

- a) Develop the truth table

- b) Write down the sum of products equation

- c) Draw the logic circuit

- d) Use Boolean algebra to simplify the equation

- e) Draw the corresponding logic circuit.

## **First Evaluation**

No. 1 Construct the truth Table

What is the Boolean equation?

No. 2 Draw the logic circuit whose Boolean equation is

$$X = (\overline{ABC})\overline{D}$$

Use the 7404, 7408 and the 7411 with pin numbers

No. 3 Simplify the following Boolean expressions

$$ABC + \overline{AB} + ABC$$

$$\overline{ABC} + AC$$

$$\overline{(A+B)}(\overline{A} + \overline{B})$$

**No. 4** A digital system has a 4 bit input from 0000 to 1111.

Design a logic circuit that produces a high output whenever the equivalent hex input is greater than C.

Truth table

Sum of products equation

Logic circuit

## <u>No. 5</u>

| Α | в | С | D | Y |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

a) Draw the Karnaugh map

b) Encircle all octets, quads, and pairs you can find.

c) What is the simplified Boolean equation?

d) Draw the logic circuit using NAND gates.

## Karnaugh Mapping – Lesson 4

## Lesson Plan

Titel: Karnaugh Mapping

Objectives:

Able to derive Karnaugh maps from a given truth tableKnow how to simplify Karnaugh maps

| Time | Method |                   | Торіс                         | Way | Remark |

|------|--------|-------------------|-------------------------------|-----|--------|

|      |        | * Review Lesson 3 |                               |     |        |

|      |        | * Ir              | ntroduction                   |     |        |

|      |        |                   | – Karnaugh map                |     |        |

|      |        | * K               | arnaugh mapping               |     |        |

|      |        |                   | - Truth table to Karnaugh map |     |        |

|                                                                  |     | – Two variable map                     |                                                                                              |                    |

|------------------------------------------------------------------|-----|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|

|                                                                  |     | – Three variable map                   |                                                                                              |                    |

|                                                                  |     | – Four variable map                    |                                                                                              |                    |

|                                                                  |     | - Pairs, Quads, and Octets             |                                                                                              |                    |

|                                                                  |     | <ul> <li>Overlapping groups</li> </ul> |                                                                                              |                    |

|                                                                  |     | <ul> <li>Rolling the map</li> </ul>    |                                                                                              |                    |

|                                                                  | * R | eview exercise                         | WS                                                                                           | Worksheet<br>No. 4 |

| S: Speech<br>D Discussion<br>Q/A: Question/Answer<br>E: Exercise |     |                                        | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO: Hands-On<br>WS: Worksheet<br>HT: Hand-Out |                    |

## Introduction

#### Karnaugh Mapping

Simplify a Boolean equation

Ex:

$$X = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C}$$

$$X = \overline{C}(\overline{A}\overline{B} + \overline{A}\overline{B} + A\overline{B} + A\overline{B})$$

$$\overline{C}_{is \ common \ in \ each \ term}$$

$$A = \overline{C}[(\overline{A}(\overline{B} + B) + A(\overline{B} + B)]$$

$$A = \overline{C}[\overline{A}(1) + A(1)]$$

$$X = \overline{C}[\overline{A}(1) + A(1)]$$

$$X = \overline{C}(\overline{A} + A)$$

$$X = \overline{C}$$

#### Karnaugh map

As you see, Boolean algebra can be used to create simpler circuits. But if you not quite familiar with Boolean theorems it is difficult to find the best simplification. Therefore Karnaugh mapping is the better alternative for simplification.

#### Truth table to Karnaugh map

The starting point for digital circuit design is usually the truth table which gives us the following information:

Under which input condition occurs a certain output condition.

Two variable map

Fig. 4–1: Two variable Karnaugh map

The truth table outputs are translated into the Karnaugh map. Each position in the map represents a certain fundamental product.

Three variable map

<u>Ex:</u>

| A                                     | В | с | x |   |    | ō | с |

|---------------------------------------|---|---|---|---|----|---|---|

| 0                                     | 0 | 0 | o | - | ĀB | 0 | 0 |

| 0                                     | 0 | 1 | o |   | ĀВ | 1 | 0 |

| 0                                     | 1 | o | 1 |   | AB | 1 | 1 |

| o                                     | 1 | 1 | o |   | ΑÐ | 0 | 0 |

| 1                                     | 0 | 0 | 0 |   |    |   |   |

| 1                                     | 0 | 1 | 0 |   |    |   |   |

| 1                                     | 1 | 0 | 1 |   |    |   |   |

| 1                                     | 1 | 1 | 1 |   |    |   |   |

| Fig. 4–2: Three variable Karnaugh map |   |   |   |   |    |   |   |

Four variable map

Many digital systems process 4 bit numbers. For this reason, logic circuits are often designed to handle 4 input variables.

<u>Ex:</u>

(see Fig. 4–3)

| Α | в | С | D       | Х        |            |              | сō    | ēρ | СD | CD |

|---|---|---|---------|----------|------------|--------------|-------|----|----|----|

| 0 | 0 | 0 | ¢       | 0        |            |              |       |    |    |    |

| 0 | o | 0 | 1       | 1        |            | ĀĒ           | 0     | 1  | ٥  | 0  |

| ٥ | 0 | í | 0       | 0        |            | <del>.</del> | o     | ۵  | 1  | 1  |

| 0 | 0 | 1 | 1       | Ο        |            | ĀВ           | Ŭ     | U  |    | ·  |

| o | 1 | 0 | 0       | O        |            | AB           | 0     | ō  | С  | 1  |

| 0 | 1 | 0 | 1       | 0        |            | _            |       | ~  |    |    |

| 0 | 1 | 1 | 0       | 1        |            | АB           | 0     | 0  | C  | Ο  |

| o | 1 | 1 | 1       | 1        |            |              |       |    |    |    |

| 1 | 0 | 0 | 0       | 0        |            |              |       |    |    |    |

| 1 | 0 | 0 | 1       | 0        |            |              |       |    |    |    |

| 1 | 0 | 1 | 0       | 0        |            |              |       |    |    |    |

| ì | ٥ | 1 | 1       | 0        |            |              |       |    |    |    |

| 1 | 1 | 0 | σ       | 0        |            |              |       |    |    |    |

| 1 | 1 | 0 | 1       | 0        |            |              |       |    |    |    |

| i | 1 | 1 | 0       | 1        |            |              |       |    |    |    |

| 1 | 1 | 1 | 1       | o        |            |              |       |    |    |    |

|   |   |   | Fig. 4- | -3: Four | variable K | arnaug       | h map |    |    |    |

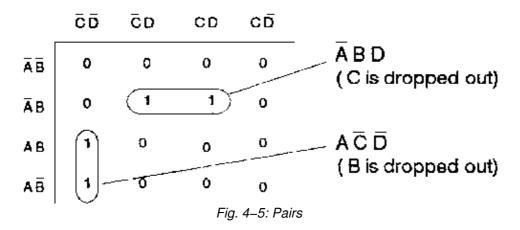

Pairs, Quads, and Octets

Pairs

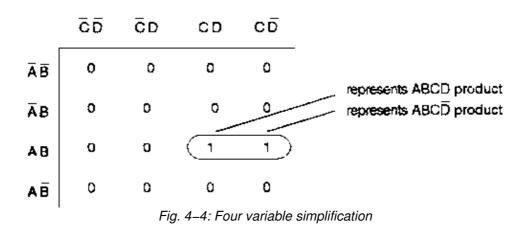

As you see in Fig. 4–4, only one variable goes from uncomplement to complement. Whenever this happens, you can eliminate the variable that changes form.

Proof:

$$X = ABCD + ABC\overline{D}$$

$X = ABC(D + \overline{D})$

Whenever you see a pair first encircle it and then simplify to get the simplified Boolean expression:

$$X = A\overline{C}\overline{D} + \overline{A}BD$$

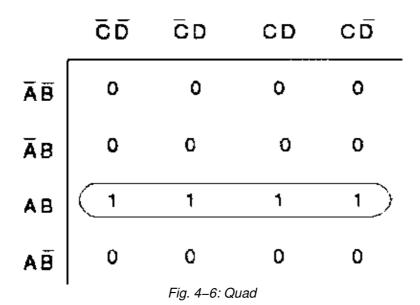

Quad

Quad: A group of 4 one's that are horizontally or vertically adjacent. End to end or in form of a square.

A quad eliminates two variables and their complements.

Proof:

$$X = ABC + ABC$$

(two pairs)

$X = AB(C + C)$

$X = AB$

Encircle the quad and step through the different one's in the quad and determine which two variables go from complement to uncomplement (or vs), these are the variables that drop out.

|    | δΰ | σõ           | CD  | сō |

|----|----|--------------|-----|----|

| ĀĒ | 0  | 0            | 0   | 0  |

| ĀВ | 0  | O            | 0   | 0  |

| AB | o  | 0            | 1   | 1  |

| ΑĐ | 0  | 0            | 1   | 1  |

|    | -  | Fig. 4–7: Qi | uad |    |

The variables B and D can be eliminated. So we get the following equation:

X = A C

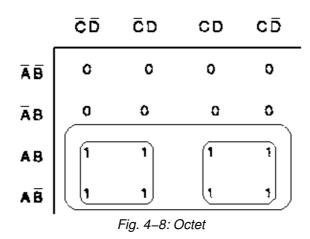

Octet

An octet eliminates three variables and their complements.

Proof:  $X = A\overline{C} + AC$  (two quads) X = A (C + C)

$\mathsf{X}=\mathsf{A}$

Karnaugh Simplifications

## Process:

- 1. Draw the Karnaugh map

- 2. Look for octets and encircle them.

- 3. Look for quads and encircle them.

- 4. Look for pairs and encircle them.

- 5. Simplify and write down the equation.

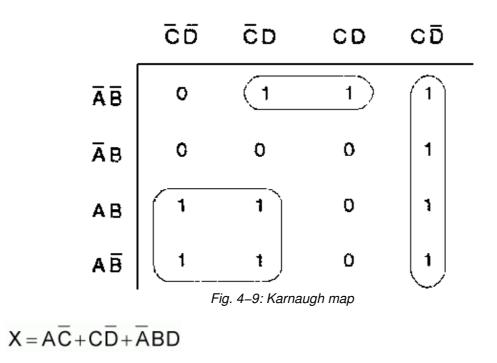

#### **Overlapping and Rolling**

Overlapping groups

<u>Ex:</u>

rig: 4–10: Karnaugh

Groups can overlap to get a simpler equation:

$$X = A + B\overline{C}D$$

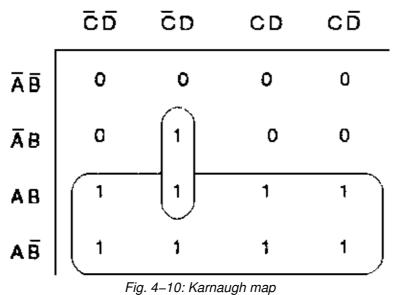

Rolling the map

Fig. 4–11: Karnaugh map

Instead of encircling two pairs:

$X = B\overline{C}D + BC\overline{D}$

We can roll the map and encircle a quad:

$$X = BD$$

Solution:

$$X = \overline{C} + \overline{A}\overline{D} + A\overline{B}D$$

Solution:

$$X = AB + AD + AC + BCD$$

# Worksheet No. 4

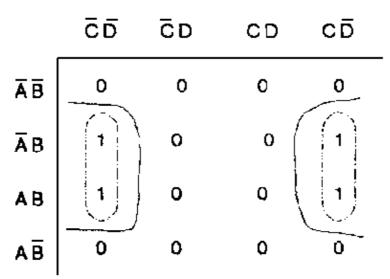

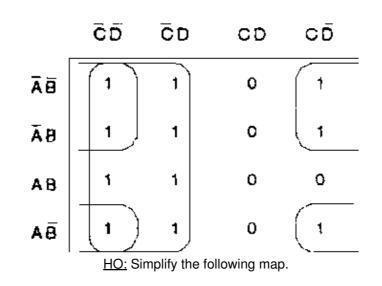

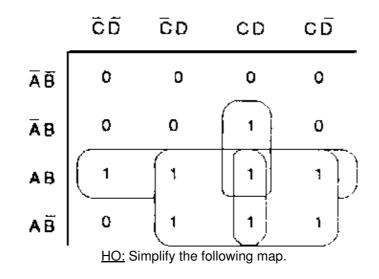

<u>No. 1</u> Simplify the following Karnaugh maps and write down the Boolean equation for every map.

|                            | $\overline{C}$ | С |

|----------------------------|----------------|---|

| $\overline{A}\overline{B}$ | 0              | 0 |

| ĀΒ                         | 1              | 0 |

| AB                         | 1              | 1 |

| $A\bar{B}$                 | 0              | 0 |

|                            | C              | С |

| ĀB                         | 1              | 1 |

| ĀΒ                         | 0              | 0 |

| AB                         | 1              | 0 |

| $A\bar{B}$                 | 1              | 1 |

|                            | C              | С |

| $\overline{A}\overline{B}$ | 1              | 0 |

| ĀΒ                         | 0              | 0 |

| AB                         | 0              | 0 |

| $A\bar{B}$                 | 1  | 0 | ) |   | -  |    |

|----------------------------|----|---|---|---|----|----|

|                            | Ē  | ) | ō | D | CD | CD |

| $\bar{A}\bar{B}$           | 0  |   |   | 1 | 0  | 0  |

| ĀΒ                         | 1  |   |   | 0 | 1  | 1  |

| AB                         | 1  |   | 0 |   | 0  | 1  |

| AB                         | 0  |   | 1 |   | 1  | 0  |

|                            | ĒĒ | 5 | ō | D | CD | CD |

| $\overline{A}\overline{B}$ | 1  |   |   | 1 | 0  | 1  |

| ĀΒ                         | 0  |   |   | 0 | 1  | 1  |

| AB                         | 0  |   | 0 |   | 0  | 1  |

| AB                         | 1  |   |   | 1 | 0  | 1  |

<u>No. 2</u> Translate each output (v, w, x, y, z) into a Karnaugh map, do the simplification and write down the Boolean equation.

| Α | в | С | D | v | w | x | у | z |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

# Lesson Plan

Titel: Karnaugh Mapping II

Objectives:

- Understand the product of sums method

- Able to use "Don't care conditions" for more effective simplifications

| Time | Method                                                            | Торіс                              | Way                                                                                          | Remark          |

|------|-------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|-----------------|

|      |                                                                   | * Review Lesson 4                  |                                                                                              |                 |

|      |                                                                   | * Introduction                     |                                                                                              |                 |

|      |                                                                   | * Product of sums method           |                                                                                              |                 |

|      |                                                                   | - Fundamental sums                 |                                                                                              |                 |

|      |                                                                   | - Product off sums simplifications |                                                                                              |                 |

|      |                                                                   | * Don't care conditions            |                                                                                              |                 |

|      |                                                                   | -Truth table                       |                                                                                              |                 |

|      |                                                                   | – Karnaugh map                     |                                                                                              |                 |

|      |                                                                   | * Review exercise                  |                                                                                              | Worksheet No. 5 |

|      | S: Speech<br>D: Discussion<br>Q/A: Question/Answer<br>E: Exercise |                                    | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO: Hands-On<br>WS: Worksheet<br>HT: Hand-Out |                 |

#### Introduction

### Karnaugh Mapping II

#### Product of sums method

Instead of using the sum of products method we can also take the product of sums method which is based on the fundamental sums:

Fig. 5–1: Truth table with fundamental sums

| Α | в | С | Х |   | Fundamental sums                      |

|---|---|---|---|---|---------------------------------------|

| 0 | 0 | 0 | 0 | ? | A+B+C                                 |

| 0 | 0 | 1 | 1 |   |                                       |

| 0 | 1 | 0 | 1 |   |                                       |

| 0 | 1 | 1 | 0 | ? | $A\!+\!\overline{B}\!+\!\overline{C}$ |

| 1 | 0 | 0 | 1 |   |                                       |

|---|---|---|---|---|---------------------------------------|

| 1 | 0 | 1 | 1 |   |                                       |

| 1 | 1 | 0 | 0 | ? | $\overline{A}\!+\!\overline{B}\!+\!C$ |

| 1 | 1 | 1 | 1 |   |                                       |

Product of sums simplification

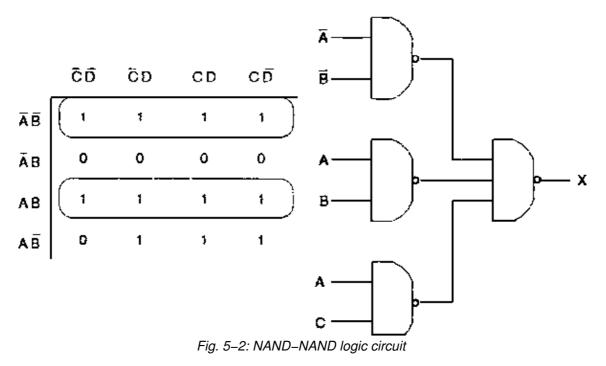

A equation gained through the sum of product method can be realized into a NAND-NAND logic circuit.

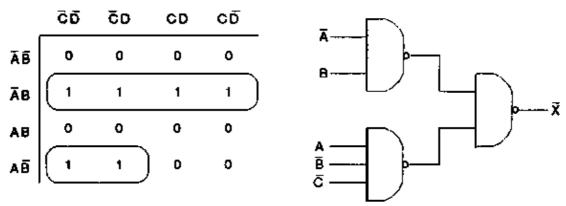

If we simplify the Karnaugh map in Fig. 5–2 we get the following equation:

$X = \overline{A}\overline{B} + AB + AC$

Based on this equation we can draw the logic circuit like in Fig. 5–2. This solution is made with the help of the sum of product method. If we want to try the product of sums method we have to go through the following steps:

1. Complement the Karnaugh map and draw the complementary NAND-NAND circuit:

Fig. 5-3: Complementary NAND-NAND circuit

The simplified equation is:

# $\overline{X} = \overline{A}B + A\overline{B}\overline{C}$

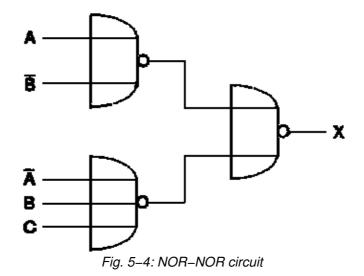

2. Convert the complementary NAND-NAND circuit to a NOR-NOR circuit:

we have changed all NAND to NOR and complemented all signals.

3. Now we got a product of sums solution for X. The last step is to compare both circuits (NAND–NAND, NOR–NOR) to find out which circuit is the simpler one, meaning the cheaper one. Because we need less gates. In our case the sum of product solution (NOR–NOR circuit) is the better solution.

### Summary of process

- 1. Convert the truth table into a Karnaugh map

- Write the sum of products equation

- Draw the NAND-NAND circuit

- 2. Complement the Karnaugh map

– Draw the complementary NAND–NAND circuit  $(\overline{X})$

- 3. Convert the complementary NAND-NAND circuit to a NOR-NOR circuit.

- Change all NAND to NOR

- Complement all signals

- 4. Compare NAND-NAND circuit with NOR-NOR circuit.

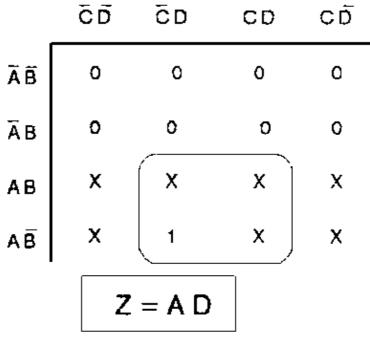

### Don't care conditions

In some digital systems, certain input conditions never occur during normal operations; therefore, the corresponding output never appears.

? It is indicated in the truth table by an X.

Fig. 5–5: Don't care conditions

| Α | в | С | D | z |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

|   | - | - |   | - |                       |

|---|---|---|---|---|-----------------------|

| 0 | 0 | 0 | 1 | 0 |                       |

| 0 | 0 | 1 | 0 | 0 |                       |

| 0 | 0 | 1 | 1 | 0 |                       |

| 0 | 1 | 0 | 0 | 0 |                       |

| 0 | 1 | 0 | 1 | 0 |                       |

| 0 | 1 | 1 | 0 | 0 |                       |

| 0 | 1 | 1 | 1 | 0 |                       |

| 1 | 0 | 0 | 0 | 0 |                       |

| 1 | 0 | 0 | 1 | 1 |                       |

| 1 | 0 | 1 | 0 | х |                       |

| 1 | 0 | 1 | 1 | х |                       |

| 1 | 1 | 0 | 0 | х | Don't care conditions |

| 1 | 1 | 0 | 1 | х |                       |

| 1 | 1 | 1 | 0 | х |                       |

| 1 | 1 | 1 | 1 | х |                       |

Don't care conditions are like wild cards, you can let them stand for what ever you like:

Fig. 5-6: Karnaugh map and simplified equation

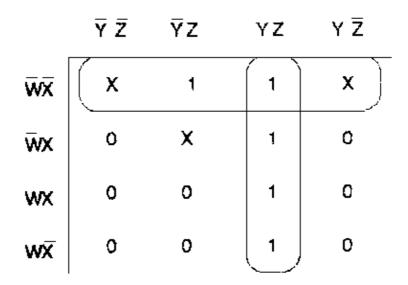

HO: Simplify the following Boolean function:

$F(w,x,y,z) = \Sigma(1,3,7,11,15)$

That has the don't care conditions:

$$d(w,x,y,z) = \Sigma(0.2,5)$$

Solution:

First we have to translate the function into a truth table:

| w | х | Y | z | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | х |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | Х |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | Х |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Now we have to convert it into a Karnaugh map and simplify it:

# Worksheet No. 5

<u>No. 1</u>

| Α | в | С | D | Y |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

a) Draw the Karnaugh map.

b) Encircle all octets, quads and pairs you can find.

c) What is the simplified Boolean equation for the Karnaugh map?

d) Draw the logic circuit.

e) Suppose the last six entries of the truth table are changed to don't cares. Using the Karnaugh map, show the simplified circuit.

f) What is the simplified NOR-NOR circuit?

# Coding – Lesson 6

### Lesson Plan

Titel: Coding

Objectives:

- Get an idea about the purpose of codes

- Understand the principle of decoder, encoder, and code converter

- Able to design logic circuits for code conversion

| Time | Method 1 | Торіс             | Way | Remark |

|------|----------|-------------------|-----|--------|

|      |          | * Review Lesson 5 |     |        |

|      |          | * Introduction    |     |        |

|      |          | * ASCII code      |     |        |

|                                                                   |     | <ul> <li>Coding scheme</li> </ul>                 |                                                                                              |                    |

|-------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|

|                                                                   |     | – Parity bit                                      |                                                                                              |                    |

|                                                                   | * B | CD code                                           |                                                                                              |                    |

|                                                                   | * E | xcess–3 code                                      |                                                                                              |                    |

|                                                                   | * G | aray code                                         |                                                                                              |                    |

|                                                                   | * E | ncoder                                            |                                                                                              |                    |

|                                                                   |     | <ul> <li>Decimal to BCD encoder</li> </ul>        |                                                                                              |                    |

|                                                                   | * D | ecoder                                            |                                                                                              |                    |

|                                                                   |     | <ul> <li>BCD to decimal decoder</li> </ul>        |                                                                                              |                    |

|                                                                   | * C | ode converter                                     |                                                                                              |                    |

|                                                                   |     | <ul> <li>BCD to Exces-3 code converter</li> </ul> |                                                                                              |                    |

|                                                                   | * R | eview Exercise                                    |                                                                                              | Worksheet<br>No. 6 |

| S: Speech<br>D: Discussion<br>Q/A: Question/Answer<br>F: Exercise |     |                                                   | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO: Hands–On<br>WS: Worksheet<br>HT: Hand–Out |                    |

### Introduction

<u>Coding</u>

Ex: Coding ? Alphanumeric information in and out of a computer.

### ASCII code

ASCII Code (American Standard Code for Information Interchange)

ASCII code is a 7 bit code whose format is

X6 X5 X4 X3 X2 X1 X0

i.e. the letter A is coded as:

100001

# Coding scheme:

|    | X6 X5 X4 |    |    |     |     |     |     |     |     |  |  |

|----|----------|----|----|-----|-----|-----|-----|-----|-----|--|--|

| ХЗ | X2       | X1 | X0 | 010 | 011 | 100 | 101 | 110 | 111 |  |  |

| 0  | 0        | 0  | 0  |     | 0   |     | Ρ   |     | Ρ   |  |  |

| 0  | 0        | 0  | 1  |     | 1   | А   | Q   | а   | q   |  |  |

| 0  | 0        | 1  | 0  |     | 2   | В   | R   | b   | r   |  |  |

|    |          |    |    |     |     |     |     |     |     |  |  |

|   | • | • | • | • | • | • | • |  |

|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |  |

| 1 | 1 | 1 | 1 |   | 0 |   |   |  |

Ex: The letter B via ASCII in binary:

### 100010

Parity bit

During sending/transmitting data, 1 bit errors may occur. To catch these errors, a parity bit is usually transmitted along with the original bits:

X7 X6 X5 X4 X3 X2 X1 X0 | parity bit

A parity checker at the receiving end can test for even or odd parity. I.e the transmitting station will set the parity bit always in that way to put the whole number in even parity. If the parity checker at the receiving end determines odd parity it will report an error message.

Now we have 8 bits (1 byte), this is the ideal length because most digital equipment is set up to handle bytes of data.

### BCD Code (Binary Coded Decimal)

Each decimal place (0...9) is represented by a binary code.

Ex: 753

0111 0101 0011

7 5 3

The BCD code is a 4 bit code which is very common along digital systems.

#### Excess-3 code

Also an important 4 bit code

Ex: Convert a decimal number in excess-3 code:

|   |     |   | 1   | 2?excess-3     |

|---|-----|---|-----|----------------|

|   | 1   |   | 2   | First we add 3 |

| + | 3   | + | 3   |                |

|   | 4   |   | 5   |                |

| 0 | 100 | 0 | 101 | Then we conve  |

101 Then we convert the sum in BCD form.

to every decimal digit.

0100 0101 in excess-3 stands for decimal 12.

Fig. 6–1: Convertion table, dec ? BCD? excess–3

| Decimal | BCD  | Excess – 3 |

|---------|------|------------|

| 0       | 0000 | 001 1      |

| 1       | 0001 | 0100       |

| 2 | 0010 | 0101 |

|---|------|------|

| 3 | 0011 | 0110 |

| 4 | 0100 | 0111 |

| 5 | 0101 | 1000 |

| 6 | 0110 | 1001 |

| 7 | 0111 | 1010 |

| 8 | 1000 | 1011 |

| 9 | 1001 | 1100 |

### Gray code

Each Gray code number differs from the preceding number by a single bit.

Fig. 6-2: Convertion table, dec ? Gray ? BCD

| Decimal | Gray | Binary |

|---------|------|--------|

| 0       | 0000 | 0000   |

| 1       | 0001 | 0001   |

| 2       | 0011 | 0010   |

| 3       | 0010 | 0011   |

| 4       | 0110 | 0100   |

| 5       | 0111 | 0101   |

| 6       | 0101 | 0110   |

| 7       | 0100 | 0111   |

| 8       | 1100 | 1000   |

| 9       | 1101 | 1001   |

#### Encoder

An encoder converts an active input signal into a coded output signal.

Ex: Decimal to BCD encoder

(see Fig. 6–3 on the next page) If switch 9 is pressed:

# A B C D = 1 0 0 1

The circuit in Fig. 6–3 is also available as TTL device 74147.

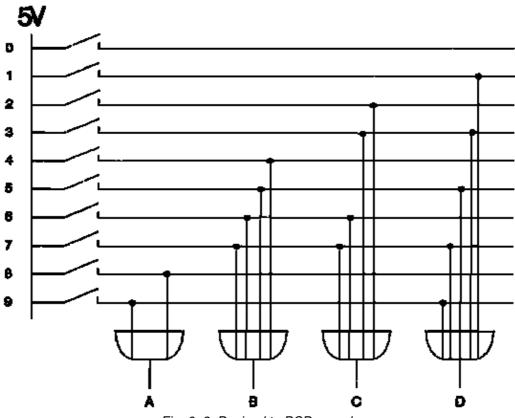

Fig. 6–3: Decimal to BCD encoder

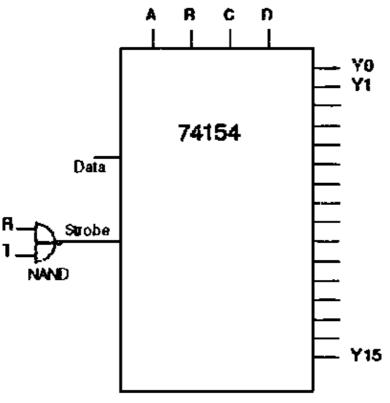

### Decoder

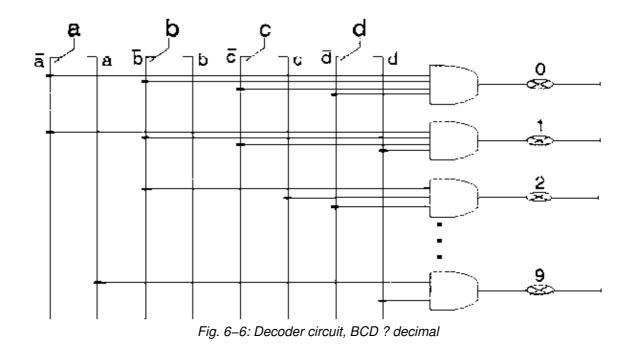

A decoder converts a coded input signal into an active output signal.

Ex: Develop a decoder circuit which converts BCD code into decimal.

Fig. 6–4: Truth table, BCD ? decimal

| а                     | b                     | с                     | d                     |     |

|-----------------------|-----------------------|-----------------------|-----------------------|-----|

| <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | <b>2</b> <sup>0</sup> | Dec |

| 0                     | 0                     | 0                     | 0                     | 0   |

| 0                     | 0                     | 0                     | 1                     | 1   |

| 0                     | 0                     | 1                     | 0                     | 2   |

| 0                     | 0                     | 1                     | 1                     | 3   |

| 0                     | 1                     | 0                     | 0                     | 4   |

| 0                     | 1                     | 0                     | 1                     | 5   |

| 0                     | 1                     | 1                     | 0                     | 6   |

| 0                     | 1                     | 1                     | 1                     | 7   |

| 1                     | 0                     | 0                     | 0                     | 8   |

| 1                     | 0                     | 0                     | 1                     | 9   |

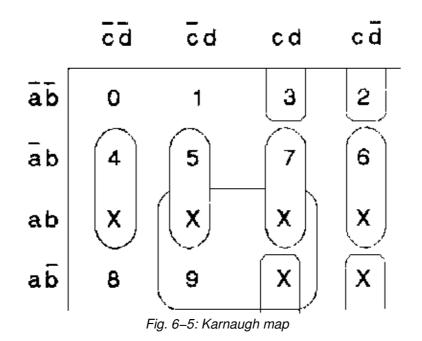

To optimize the circuit we use a Karnaugh map for simplification:

For every number in the Karnaugh map we can write an equation:

X0=abcdX1=abcdX2=bcdX3=bcdX4=bcdX5=bcdX6=bcdX7=bcdX8=abcdX9=ad

Now we can draw the logic circuit:

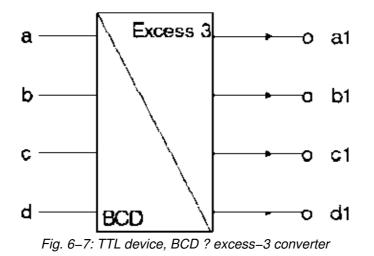

#### Code converter

Code converter are logical networks which convert codes into another.

Fig. 6–8: Convertion table, dec ? BCD? excess–3

| Dec |   | BC | D |   | Excess – 3            |                |                       |                |

|-----|---|----|---|---|-----------------------|----------------|-----------------------|----------------|

|     | а | b  | е | d | <b>a</b> <sub>1</sub> | b <sub>1</sub> | <b>C</b> <sub>1</sub> | d <sub>1</sub> |

| 0   | 0 | 0  | 0 | 0 | 0                     | 0              | 1                     | 1              |

| 1   | 0 | 0  | 0 | 1 | 0                     | 1              | 0                     | 0              |

| 2   | 0 | 0  | 1 | 0 | 0                     | 1              | 0                     | 1              |

| 3   | 0 | 0  | 1 | 1 | 0                     | 1              | 1                     | 0              |

| 4   | 0 | 1  | 0 | 0 | 0                     | 1              | 1                     | 1              |

| 5   | 0 | 1  | 0 | 1 | 1                     | 0              | 0                     | 0              |

| 6   | 0 | 1  | 1 | 0 | 1                     | 0              | 0                     | 1              |

| 7 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

# Worksheet No. 6

No. 1 Develop a decoder circuit for the conversion of the Gray code into the decimal system. Use a Karnaugh map to get a simplified circuit!

| G | ray | coc | le | decimal |

|---|-----|-----|----|---------|

| d | C   | b   | а  |         |

| 0 | 0   | 0   | 0  | 0       |

| 0 | 0   | 0   | 1  | 1       |

| 0 | 0   | 1   | 1  | 2       |

| 0 | 0   | 1   | 0  | 3       |

| 0 | 1   | 1   | 0  | 4       |

| 0 | 1   | 1   | 1  | 5       |

| 0 | 1   | 0   | 1  | 6       |

| 0 | 1   | 0   | 0  | 7       |

| 1 | 1   | 0   | 0  | 8       |

| 1 | 1   | 0   | 1  | 9       |

| х | Х   | Х   | Х  |         |

|   |     |     | •  |         |

|   |     |     |    |         |

No. 2 Develop a code converter for the conversion of the excess 3 code into the 8421 code (BCD).

Complete the truth table!

Use Karnaugh maps to get a simplified circuit!

| Exc | ess | s 3 ( | cod | 8421 code |    |    |    |    |

|-----|-----|-------|-----|-----------|----|----|----|----|

| dec | d   | с     | b   | а         | d1 | c1 | b1 | a1 |

| 0   | 0   | 0     | 1   | 1         | 0  | 0  | 0  | 0  |

| 1   | 0   | 1     | 0   | 0         | 0  | 0  | 0  | 1  |

| 2   | 0   | 1     | 0   | 1         | 0  | 0  | 1  | 0  |

| 3   | 0   | 1     | 1   | 0         | 0  | 0  | 1  | 1  |

| 4   | 0   | 1     | 1   | 1         | 0  | 1  | 0  | 0  |

| 5   | 1   | 0     | 0   | 0         | 0  | 1  | 0  | 1  |

| 6   | 1   | 0     | 0   | 1         | 0  | 1  | 1  | 0  |

| 7   | 1   | 0     | 1   | 0         | 0  | 1  | 1  | 1  |

| 8 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|

| 9 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

|   | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

|   | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

|   | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

|   | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

|   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

|   | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

The lower six rows are redundant.

# Flip-Flops – Lesson 7

### Lesson Plan

Titel: Flip-Flops

Objectives:

- Understand the Flip-Flop principleKnow the three basic Flip-Flops (RS, D, JK)

- Able to analyze timing diagrams

| Time | Method                                                            | Торіс               | Way                                                                                          | Remark             |

|------|-------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|--------------------|

|      |                                                                   | * Review Lesson 6   |                                                                                              |                    |

|      |                                                                   | * Introduction      |                                                                                              |                    |

|      |                                                                   | * RS Flip–Flops     |                                                                                              |                    |

|      |                                                                   | * Clocked RS-FF     |                                                                                              |                    |

|      |                                                                   | * Timing diagram    |                                                                                              |                    |

|      |                                                                   | * D–FF              |                                                                                              |                    |

|      |                                                                   | * FF switching time |                                                                                              |                    |

|      |                                                                   | * JK–FF             |                                                                                              |                    |

|      |                                                                   | * JK-MS-FF          |                                                                                              |                    |

|      |                                                                   | * Review exercise   |                                                                                              | Worksheet<br>No. 7 |

|      | S: Speech<br>D: Discussion<br>Q/A: Question/Answer<br>F: Exercise |                     | B: Boardscript<br>P: Picture<br>Ex: Example<br>HO: Hands–On<br>WS: Worksheet<br>HT: Hand–Out |                    |

#### Introduction

#### Flip-Flops

Sometimes there is a need of digital devices or circuits whose output will remain unchanged, once set, even if there is a change in input.

### **RS Flip-Flops**

A Flip-Flop is a bistable electronic circuit that has two stable states.

? Output is either 0 or 5V dc

The Flip-Flop can be regarded as a memory device. It can be used to store one binary digit at the output.

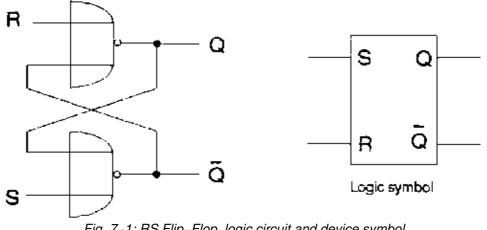

Fig. 7–1: RS Flip–Flop, logic circuit and device symbol

HO: What is the truth table for the circuit above?

### Solution:

Fig. 7–2: Truth table, RS Flip–Flop

| R | S | Q          | Action    |

|---|---|------------|-----------|

| 0 | 0 | Last value | No change |

| 0 | 1 | 1          | Set       |

| 1 | 0 | 0          | Reset     |

| 1 | 1 | ?          | Forbidden |

If both inputs (R, S) are high at once, the output can not be determined before; therefore, it is a forbidden state.

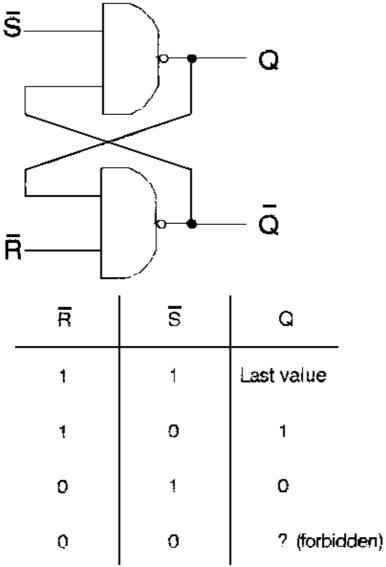

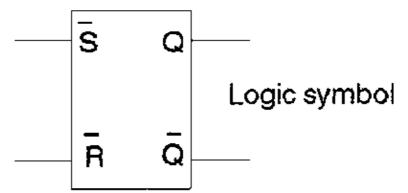

Ex: Create a RS Flip-Flop with NAND gates.

Fig. 7–3: RS Flip–Flop with NAND gates

*Note:* The inputs (R, S) are indicated with an overbar so they are inverted.

Fig. 7-4: Logic symbol, RS Flip-Flop with inverted inputs

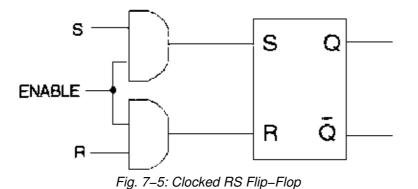

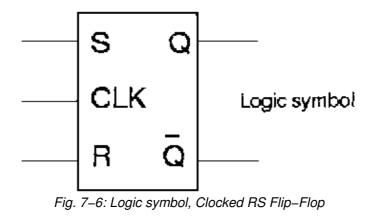

Clocked RS Flip-Flop

This Flip–Flop ca be enabled or disabled.

ENABLE ? low: R and S will have no effect on the output

ENABLE ? high: R and S inputs will be directly transmitted to the output

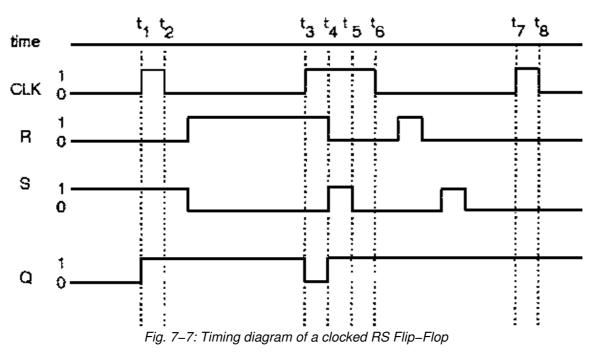

Timing diagram

A timing diagram is a drawing to determine the time dependent actions of logic devices.

Fig. 7–7 shows that the inputs (R, S) effect the output (Q) only when the clock signal (CLK) is high.

RS Flip-Flop application: Bounce free switch

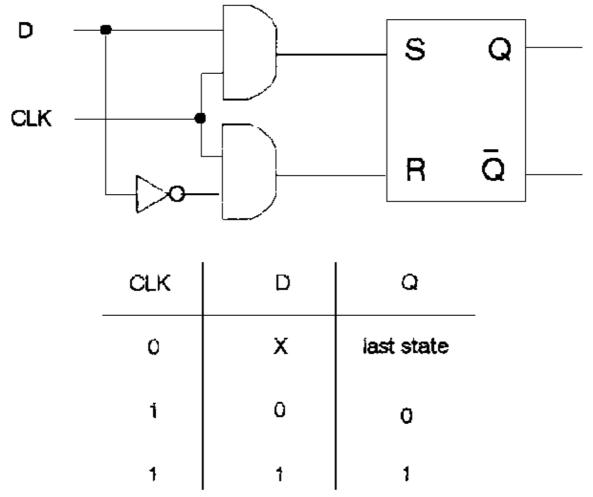

### D – Flip–Flop (D–FF)

The generation of two signals to drive a Flip–Flop is a disadvantage in many applications. This has led to the D–FF, a circuit that needs only a single data input.

Fig. 7-8: D Flip-Flop, logic circuit and truth table

CLK ? low: D can change without effect on the output

CLK ? high: Q is forced to equal the value of D

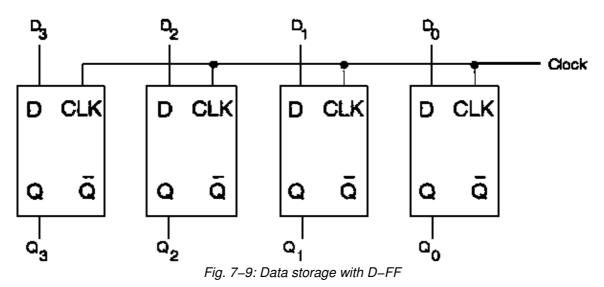

Ex: Create a 4 bit data memory with D-latches (D-FF).

In Fig. 7–9, when the clock goes high, input data is loaded into the Flip–Flops and appears at the output.

Suppose the data input is:

$D_3 D_2 D_1 D_0 = 1010$

When the clock goes high this 4 bit word is loaded into the D-latches, resulting in an output of:

$$Q_3 Q_2 Q_1 Q_0 = 1 \ 0 \ 1 \ 0$$

Flip-Flop switching time

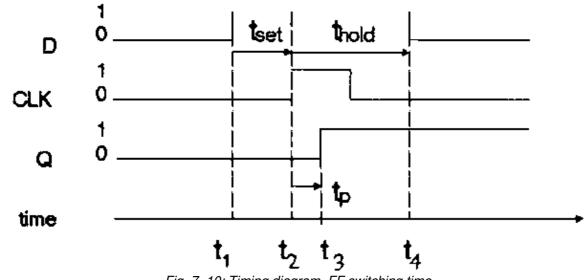

Fig. 7–10: Timing diagram, FF switching time

- t<sub>set</sub>: Minimum of time that the date bit must be present before the clock edge hits (because of stray capacitance)

- $t_{\text{hold}}$ : The data bit has to be hold long enough for the internal transistors to switch.

- $t_{o}$ : Switching time, diodes and transistors cannot switch states immediately. (some nanoseconds)

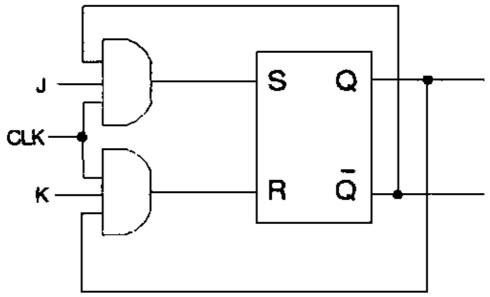

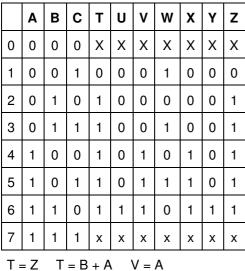

# JK Flip-Flop (JK-FF)

Flip – Flops can be used to build counters, JK–FF are the ideal elements for that purpose.

Fig. 7–11: JK–FF, logic circuit

Ex: What is the truth table for the circuit above?

Fig. 7–12: Truth table, JK-FF

| CLK        | J | κ | Q          |

|------------|---|---|------------|

| Х          | 0 | 0 | last state |

| $\uparrow$ | 0 | 1 | 0          |

| $\uparrow$ | 1 | 0 | 1          |

| $\uparrow$ | 1 | 1 | toggle     |

J and K ? low: Both AND gates are disabled, clock pulses have no effect. Q retains its last value.

J?low, K? The upper gate is disabled, only reset is possible (unless Q is already reset). high:

J?high, K? The lower gate is disabled, only set is possible (unless Q is already high). low:

J and K ? Set or reset is possible, the Flip-Flop will "toggle" on the next positive clock edge. Toggle high: means to switch to the opposite state.

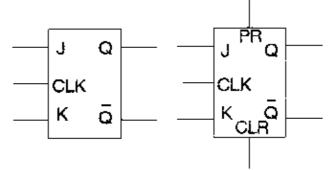

Fig. 7-13: JK-FF's, logic symbols

Preset (PR) and Clear (CLR) are input signals to get a definite start point.

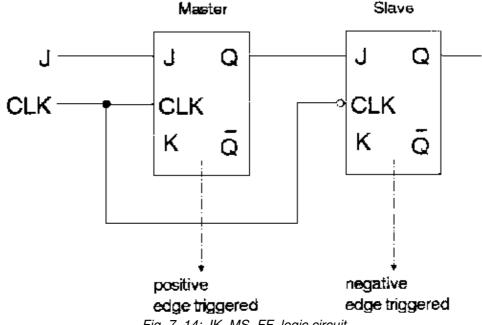

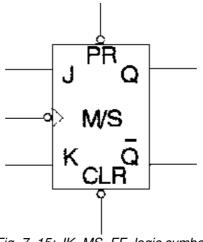

JK Master-Slave FF (JK-MS-FF)

Fig. 7-14: JK-MS-FF, logic circuit

Regardless what the master does, the slave copies it. The slave copies the master on the negative clock edge. This circuit provides a way to avoid racing.

Fig. 7–15: JK–MS–FF, logic symbol

### Available as TTL device: 74 LS 76

### Worksheet No. 7

**No. 1** A JK master slave FF has its inputs tied to + 5V, and a series of pulses are applied to its CLK input Describe the Q output.

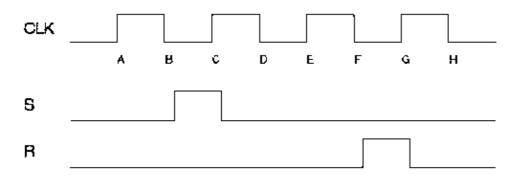

**No. 2** The signal drives a clocked RS – FF. If Q is low before point A in time: At what point does Q becomes a 1? What does Q reset to 0?

No. 3 Use the information in the preceding problem and draw the waveform Q.

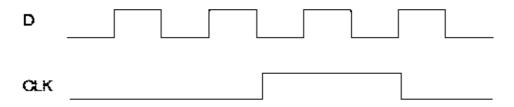

No. 4 The signal drives a D-FF. What is the value of stored in the FF after the clock pulse is over?

**No. 5** A normal JK–FF, J = K = 1. A 1 MHz is applied to the CLK input it has a propagation delay  $t_p$  of 50 ns. Draw the input squarewave and the out put expected at Q. Be sure to show the propagation delay time.

# **Second Evaluation**

No. 1 In a workshop two machines are driven by an electric motor

Power consumption: motor A = 1 KW

motor B = 2 KW

For a new machine of which its motor C receives the power of 4 KW, the maximum main power of Pmax = 4 KW is sufficient only if the two other machines (A and B) are not switched on. Design a circuit which supplies a warning signal Q if a power higher than 4 KW is taken from the main power system by the three machines.

- Truth table

- Karnaugh map

- Logic circuit

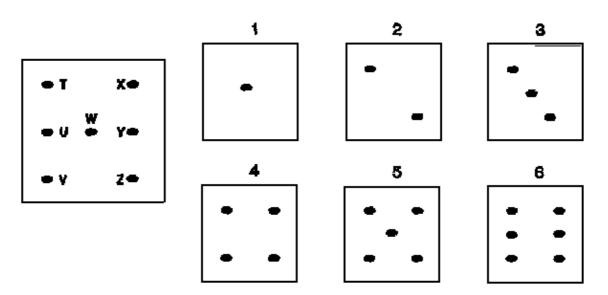

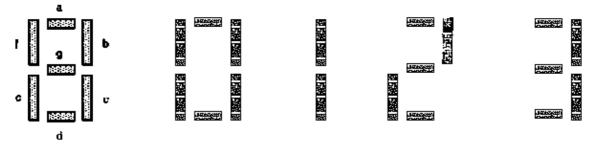

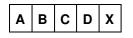

<u>No. 2</u> For a display of the figures 1–6, in the well known spot configuration of a game die, design the code conversion circuit. At the input the figures are binary coded.

- T, U, V, W, X, Y, Z are output variables (LED's)

- Truth table

- Karnaugh map

- Logic circuit

No. 3 Design a JK Flip Flop with NAND and AND gates.

- Logic circuit

- Truth table

No. 4 Design a D Flip Flop. Use only NAND gates.

- Logic circuit

- Truth table

# Counter – Lesson 8

# Lesson Plan

Titel: Counter

Objectives:

- Understand the principle of asynchronous and synchronous counter

- Able to design asynchronous counter

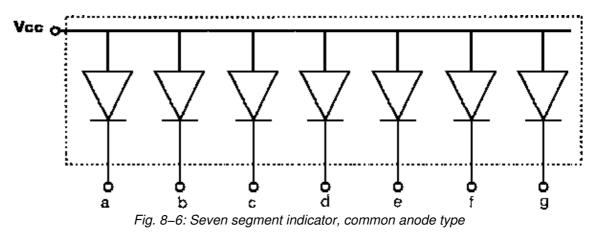

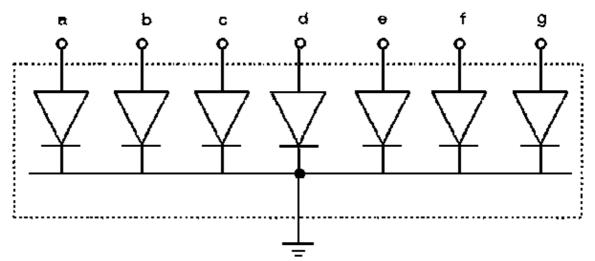

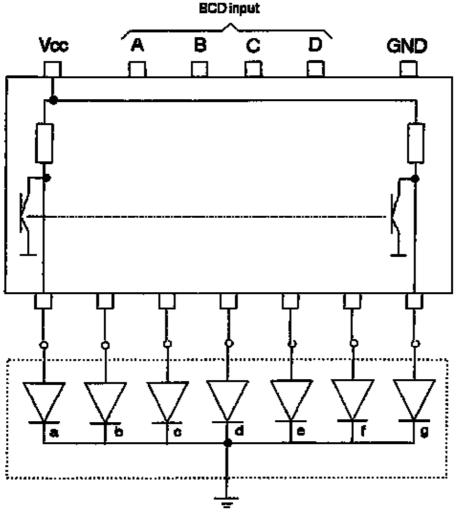

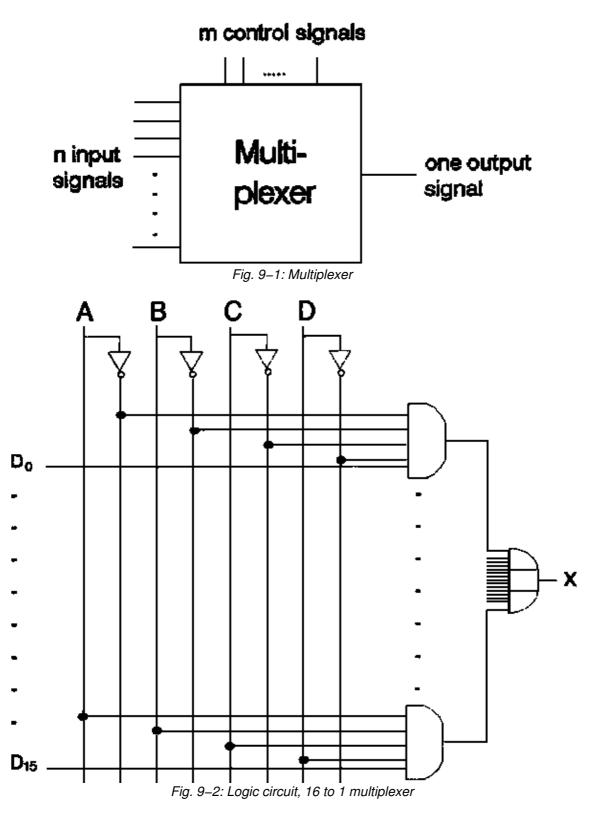

- Know the seven segment principle

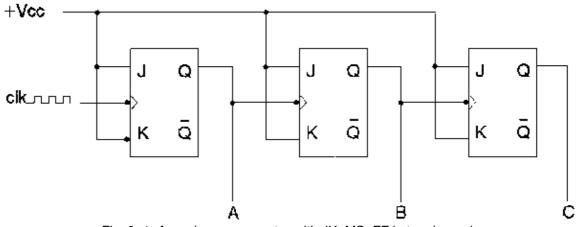

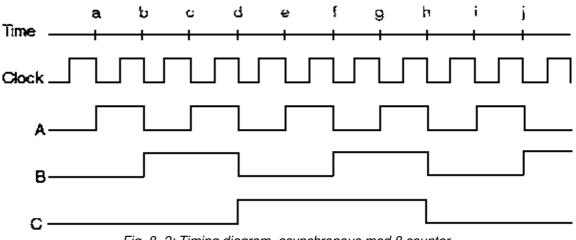

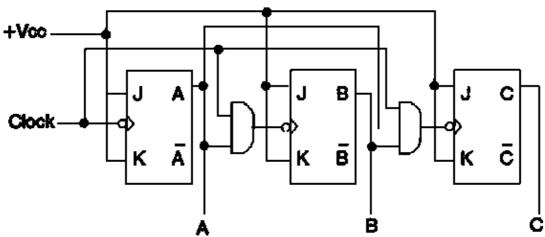

| Time | Method                                                            |                                       | Торіс                                     | Way                                                                                          | Remark             |

|------|-------------------------------------------------------------------|---------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|

|      |                                                                   | * F                                   | Review Lesson 7                           |                                                                                              |                    |