# ESA/390 Enhanced Floating Point Support: An Overview

SHARE 93, Summer Meeting 1999, Session 8163

John R. Ehrman

IBM Santa Teresa Laboratory

IBM Software Systems Division

555 Bailey Avenue/F4

San Jose, California 95141

Internet: ehrman@vnet.ibm.com

August, 1999

| Overview                                            | . 2 |

|-----------------------------------------------------|-----|

| Floating Point Data: Representations and Behavior   | 2   |

|                                                     |     |

| The Reality of Realistic Data                       |     |

| Computing With Numeric Data                         |     |

| Basic Floating Point Representations                |     |

| Terminology                                         |     |

| Machine Representations of Floating Point Numbers   |     |

| A Sampling of Floating Point Representations        |     |

| Real Numbers vs. Floating-Point Numbers             | 13  |

|                                                     |     |

| Consequences of Finite Precision                    |     |

| Precision Properties of Floating-Point Numbers      |     |

| Rounding                                            |     |

| Conversions To and From Decimal                     |     |

| How Many "Significant Digits"?                      | 19  |

| Consequences of Finite Bongs                        | 24  |

| Consequences of Finite Range                        |     |

| Value Ranges                                        |     |

| Exponent Range: Representable and Computable Values |     |

| Overflow and Underflow                              |     |

| Handling Overflow and Underflow                     |     |

| Meaningless Computations                            | 26  |

| Real-Mathematics Fictions, Floating-Point Facts     | 27  |

| ·                                                   |     |

| The Laws of "Real" Arithmetic                       | ZŎ  |

|    | Real vs. Realistic (Floating Point) Arithmetic        | 30 |

|----|-------------------------------------------------------|----|

|    | Floating Point Arithmetic Considerations              | 31 |

|    | The Facts of Floating Point Arithmetic                |    |

|    | The Facts of Floating Point Arithmetic: Consequences  |    |

|    | The Facts of Floating Point Arithmetic: Inequalities  |    |

|    | Floating Point Pecularities and Pathologies           |    |

|    | Why Does Floating Point Work At All?                  |    |

|    | Some General Conclusions                              |    |

|    |                                                       |    |

| Α  | Review of IBM Hex Floating Point                      | 44 |

|    | IBM Hex Floating Point                                |    |

|    |                                                       |    |

| IE | EEE Floating Point Standard                           | 48 |

|    | IEEE Floating Point Standard: Representations         |    |

|    | IEEE Floating Point Standard: Normal Values           | 50 |

|    | IEEE Floating Point Standard: Special Values          |    |

|    | IEEE Floating Point: Full Range of the Representation |    |

|    | IEEE Floating Point Standard: Required Capabilities   | 56 |

|    | IEEE Floating Point Standard: Further Details         |    |

|    | IEEE Floating Point Standard: Recommended Functions   |    |

|    | IEEE Floating Point Standard: Justifications          |    |

|    |                                                       |    |

| Ε  | SA/390 Floating Point Enhancements                    | 64 |

|    | ESA/390 Floating Point Enhancements: Overview         |    |

|    |                                                       |    |

| ESA/390 Hardware Enhancements                                | 66 |

|--------------------------------------------------------------|----|

| ESA/390 Floating Point Enhancements: Processor Features      | 67 |

| ESA/390 Floating Point Enhancements: BFP Data Types          | 68 |

| ESA/390 Floating Point Control Register                      | 70 |

| ESA/390 Floating Point Enhancements: Rounding Modes          | 73 |

| ESA/390 HFP Enhancements                                     | 74 |

| ESA/390 Floating Point Support Instructions                  | 75 |

| ESA/390 Floating Point Enhancements: BFP Instructions        | 77 |

| ESA/390 Floating Point Enhancements: Control Instructions    | 86 |

| ESA/390 Software Enhancements                                | 87 |

| OS/390 Operating System Support                              |    |

| ESA/390 Floating Point: HLASM Support                        |    |

| ESA/390 Floating Point: HLASM Toolkit Feature Support        | 94 |

| C/C++ Compiler Support                                       | 95 |

| C/C++ and LE Runtime Library Support                         | 97 |

| Java Language Definition                                     | 99 |

| Java Support: Implementations 1                              | 00 |

| Other Products' Support                                      | 01 |

| ESA/390 Floating Point Software Conventions                  | 02 |

| Contrasting Binary and Hexadecimal Floating Point on ESA/390 | 05 |

| Binary and Hex Floating Point: General Differences           | 06 |

| Binary and Hex Floating Point: Representation Differences    | 80 |

| Binary and Hex Floating Point: Computational Differences     | 09 |

| Binary vs. Hex Floating Point: 4-Byte (Short) Precision      | 10 |

| Binary vs. Hex Floating Point: 8-Byte (Long) Precision      | 111 |

|-------------------------------------------------------------|-----|

| Binary vs. Hex Floating Point: 16-Byte (Extended) Precision | 112 |

| IEEE vs. IBM Hex Floating Point: Exception Differences      |     |

| Other IEEE Implementations                                  | 114 |

| General Observations                                        |     |

| Intel                                                       | 116 |

| RISC System/6000                                            | 118 |

| Binary and Hexadecimal: Differences to Watch Out For        | 120 |

| Standard Conformance and Language Issues                    | 121 |

| Coding Implications                                         |     |

| Compiling and Optimization Implications                     | 123 |

| Library/Run-Time Issues                                     |     |

| Summary                                                     | 126 |

| References                                                  | 128 |

#### **Trademarks**

The following are trademarks or registered trademarks of the International Business Machines Corporation or other companies:

- IBM

- System/360

- System/370

- System/390

- S/360

- S/370

- S/390

- ESA/390

- OS/390

- DEC

- VAX

- Alpha

- HP

- PA-RISC

- SUN

- SPARC

#### **Overview**

- Why floating point?

- About floating point: precision, range, and the like

- How floating point arithmetic differs from "real" arithmetic

- IBM hexadecimal floating point

- The IEEE Floating Point Standard

- ESA/390 and OS/390 floating point support

- ESA/390 hardware enhancements

- OS/390 software enhancements

- Contrasting binary and hexadecimal floating point on ESA/390

- Usage and migration considerations

- Other IEEE floating point implementations

- Summary

Floating Point Data:

Representations and Behavior

#### The Reality of Realistic Data

Numeric data comes in all sizes:

```

6023 00000 00000 00000 00000.

Avogadro's Number

9 46000 00000 00000.

meters/light-year

2997 76000.

meters/sec (light)

33136.

cm/sec (sound)

745.7

Watts/horsepower

hertz (Concert A)

440.

cc/cubic inch

16.3872

3.14159 26535 89793

\pi

kilometers/mile

1.60935

1n 2

.69314 71805 59945

Coulombs/electron

.00000 00000 00000 00016

Planck's const (erg-sec)

.00000 00000 00000 00000 00000 06624

grams/electron

.00000 00000 00000 00000 00000 00910 7

```

Programs must manage these widely varying magnitudes

#### **Computing With Numeric Data**

- Early computers provided only integer arithmetic

- "Reals" were approximated by scaled fixed-point numbers

- Programmers (or compilers) keep track of the radix point

- Fixed point requires "shifts" for re-scaling after some operations

- Still used for decimal arithmetic (e.g., COBOL, PL/I)

- Problems: handling full range of values; maximizing precision

- Magnitude overflow loses the <u>most</u> significant digits

- Truncation of low-order (least significant) digits loses precision

- Full field width (to handle full range of values) cannot retain full precision for normal (non-extreme) values

#### Computing With Numeric Data ...

Solution: floating point!

"For each arithmetic operation we ask the computer to present us with the first few significant digits and the count telling us where the decimal point lies. These operations are referred to as floating point arithmetic." (Sterbenz, p.4)

- Increased, more uniform precision

- Precision losses involve the <u>least</u> significant digits

- That's the way most of us do arithmetic...

- Manages scaling automatically

- Hardware keeps track of the radix point for you

- Much less likelihood of "magnitude overflow"

#### **Basic Floating Point Representations**

- Floating Point numbers are a subset of the rational numbers

- A value X is represented by ± M × r<sup>k</sup>

- **M** an integer satisfying  $0 \le M < r^p$

- r radix (or base) of the representation

- p precision (the number of base-r digits)

- k exponent

- The set of all such values is a **floating point system FP(r,p)**

- Examples using FP(10,4):

#### **Basic Floating Point Representations ...**

- If a number is not exactly representable, it must be approximated by one

of the nearest representable values

- Approximations using FP(10,4):

| Rounded Down     | Rounded Down     | Rounded Up       |

|------------------|------------------|------------------|

| 3 3 3 3.         | 6 6 6 6.         | 6 6 6 7.         |

| k = -4 $X = 1/3$ | k = -4 $X = 2/3$ | k = -4 $X = 2/3$ |

- Examples of base-16 and base-2 representations of 0.1 (base 10):

- in FP(16,6):  $1677722/16^6 = 1677722/16777216 = 0.10000002384$

- in FP(2,24):  $13421773/2^{27} = 13421773/134217728 = 0.10000000149$

- Decimal fractions aren't generally precisely representable in base 2

#### **Basic Floating Point Representations ...**

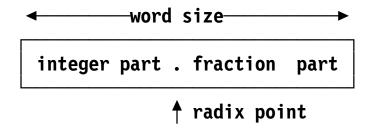

- Common practice: use a <u>fraction</u>  $f = M \div r^p$  satisfying  $0 \le f < 1.0$

- Puts the radix point at the left end of the digits

- X is then represented by  $\pm$  f  $\times$  r<sup>e</sup>

- e = k + p

- If f is <u>normalized</u>,  $r^{-1} \le f < 1.0$  (most significant digit  $\ne 0$ )

- Examples of normalized and unnormalized representations:

| normalized | unnormalized | normalized | unnormalized | unnormalized |

|------------|--------------|------------|--------------|--------------|

| .1 2 3 0   | .0 1 2 3     | .7 3 0 0   | .0 7 3 0     | .0 0 7 3     |

| k = 3      | k = 4        | k = 2      | k = 3        | k = 4        |

| X = 123    | X = 123      | X = 73     | X = 73       | X = 73       |

- Unnormalization allows redundant representations!

- May also have many redundant representations of zero

#### **Terminology**

- A floating-point number (say, 123.45E-67) is composed of two parts:

- 1. the "number stuff" (the 123.45)

- 2. the "exponent stuff" (the E-67)

- Fraction: some or all of the digits of the "number stuff"

- DEC™ VAX™ and IEEE store "some" digits (all but one implicit bit)

- IBM hex float stores "all" digits

- Sometimes called "mantissa" (but that word comes from logarithms...)

- **Significand:** the "number stuff," with <u>all</u> numerically significant digits exposed; what the machine actually calculates with

- Exponent: the "exponent stuff," correctly signed

- Characteristic, Biased Exponent: exponent+bias

- The bias is chosen so that valid values of the exponent cause the biased exponent to be always non-negative

#### **Machine Representations of Floating Point Numbers**

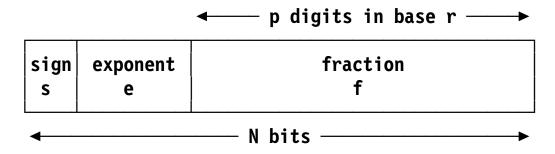

- Many ways to "package" the pieces into a "representation"

- Example of a typical format:

- Typically, fraction sign s = 0 means +, s = 1 means -

- e is almost always represented in binary

- May be signed or unsigned

- f may be sign-magnitude, radix-complement, etc.

- Finiteness imposes limits on both p and the range of e

- This finiteness has many interesting consequences...

- Designers must choose among base, precision, exponent width/range

- Number of distinct values  $\leq 2^{N}$  (and may be **much**  $< 2^{N}$ )

# A Sampling of Floating Point Representations

| Machines and                | Base | Base-B | Equiv. | Exp.  | Format | Fraction         |

|-----------------------------|------|--------|--------|-------|--------|------------------|

| Representations             | (B)  | Digits | Decm1. | Width | (Note) | Representation   |

| Pr1me 550 series single     | 2    | 23     | 6      | 8     | s/f/e  | Two's—complement |

| IEEE Standard single        | 2    | 24     | 6      | 8     | s/e/f  | Sign-magnitude   |

| DEC VAX F—format            | 2    | 24     | 6      | 8     | s/e/f  | Sign-magnitude   |

| IBM System/370 short        | 16   | 6      | 6      | 7     | s/e/f  | Sign-magnitude   |

| Burroughs 6700/7700         | 8    | 13     | 10     | 7     | s/e/i  | Sign-magnitude   |

| Harris Series 500 double    | 2    | 38     | 11     | 8     | s/f/e  | Two's-complement |

| Pr1me 550 series double     | 2    | 47     | 13     | 16    | s/f/e  | Two's-complement |

| CDC 6600/CYBER 70           | 2    | 48     | 14     | 11    | i/e/s  | One's-complement |

| Cray—2 single               | 2    | 48     | 14     | 15    | s/se/f | Sign-magnitude   |

| DEC VAX G—format            | 2    | 52     | 15     | 11    | s/e/f  | Sign-magnitude   |

| IEEE Standard double        | 2    | 53     | 15     | 11    | s/e/f  | Sign-magnitude   |

| IBM System/370 long         | 16   | 14     | 15     | 7     | s/e/f  | Sign-magnitude   |

| DEC VAX D—format            | 2    | 55     | 16     | 8     | s/e/f  | Sign-magnitude   |

| Harris Series 500 quadruple | 2    | 69     | 22     | 23    | s/f/e  | Two's-complement |

| Cray—2 double               | 2    | 96     | 28     | 15    | s/se/f | Sign-magnitude   |

| IBM System/370 extended     | 16   | 28     | 32     | 7     | s/e/f  | Sign-magnitude   |

| DEC VAX H—format            | 2    | 112    | 33     | 15    | s/e/f  | Sign-magnitude   |

Note: s = sign, se = signed exponent, e = exponent, f = fraction, i = integer.

#### Real Numbers vs. Floating-Point Numbers

- "Real" numbers are mathematical abstractions: useful, but unreal

- Abstract numbers have no inherent precision or size limitations

- Real computations are done with "realistic," "actual" numbers

- Always have finite precision and accuracy

- Must discard "excess" digits somewhere

- You <u>must</u> think differently about floating point numbers and arithmetic:

- Finite range and precision imply violation of mathematical "laws"

- Floating point numbers don't satisfy all the mathematical properties of rationals

- Nor those of mathematical "reals" (We'll see later how close they come...)

# Consequences of Finite Precision

#### **Precision Properties of Floating-Point Numbers**

- Useful measure: the ulp (unit in the last place)

- ulp(x) = successor(x) x ("spacing" between neighbors)

- relative ulp-error(x) = ulp(x) / x (weight assigned to lowest-order bit of x)

- Adding 1 in the low-order digit position has an effect that varies between  $r^{-p}$  and  $r^{-(p-1)}$

- Compare (0.999-0.998) to (0.101-0.100): **relative ulp** varies from  $10^{-3}$  to  $10^{-2}$

- Thus, relative-ulp(x) varies by a factor r, as x varies by powers of r

- This effect is known as "wobbling precision"

- Precision (relative) is not properly measured as r-p

- Magnitude of a normalized fraction varies from  $1-r^{-p}$  ( $\approx 1$ ) to  $r^{-1}$  (i.e., by a factor of r)

- Hence, relative precision is better approximated as  $r^{-(p-1)}$

- This affects how closely floating point arithmetic approximates "real" (i.e., unrealistic) arithmetic

#### Rounding

- Finite precision requires some treatment of "excess" digits

- Consider the value 2/3 = 0.666666... in FP(10,4):

- 1. Throw away the excess: result = 0.6666

- Called "chopping" or "truncating" or "rounding toward zero"

- 2. Round towards  $+\infty$ : +2/3 becomes 0.6667, -2/3 becomes -0.6666

- 3. Round towards  $-\infty$ : +2/3 becomes 0.6666, -2/3 becomes -0.6667

- 4. Round to nearest can be done two ways:

- a. Add correctly signed 1/2 ulp ("biased round to nearest")

- 0.12345 rounds to 0.1235

- The mode used by DEC VAX arithmetic, IBM hex rounding instructions

- b. For values exactly half-way between to representables, choose the result that ends in an even digit ("unbiased round to nearest")

- 0.12345 rounds to 0.1234

- Why is traditional rounding "biased"? In FP(10,4), perform X=(X-Y)+Y repeatedly, starting with X=1.000, Y=-0.5555:

- Biased round yields: 1.001, 1.002, 1.003, ...

- Unbiased round yields: 1.000, 1.000, 1.000, ...

#### **Conversions To and From Decimal**

- "IN" conversion: from decimal to machine radix

- "OUT" conversion: from machine radix to decimal

- Equivalent decimal digits: (an "IN-OUT" conversion definition):

- In a floating point system FP(r,p) with radix r and p base-r digits:

- If (1)  $10^{J} \neq r^{K}$  for any (J,K), and

- (2) All d-digit decimal floating-point numbers can be converted <u>to</u> a member of FP(r,p), and when converted <u>back</u> to decimal will correctly recover the original decimal value,

**Then** FP(r,p) can faithfully represent d-digit decimal numbers.

- (This is the definition used for the table on slide 12)

- Recoverability requires <u>all</u> conversions to be correctly rounded

#### Conversions To and From Decimal ...

Examples using S/390 short (6-digit) hex floating point:

- All 6-digit decimal floating point values can be converted to hex and back with complete recovery

- Even though  $16^{-6} \approx 0.59 \times 10^{-7}$ , not all 7-digit decimal floating point values can be recovered!

- $-16^{-5} \approx 0.95 \times 10^{-6}$  is a better "precision" estimate

- The six 7-digit decimal floating point values 0.625000<u>x</u>E-1 (where <u>x</u>=3 ... 8) are all represented by X'40100001'.

- X'40100001' converted back to decimal gives 0.6250006E-1

# **How Many "Significant Digits"?**

"IN-OUT" conversions: start with external decimal data, convert to internal format, and back to decimal

**IN-OUT Conversions**

| Precision | Decimal<br>Digits | Hex<br>Digits | Binary<br>Digits |

|-----------|-------------------|---------------|------------------|

| short     | 6                 | 6             | 21               |

| long      | 15                | 14            | 51               |

| extended  | 32<br>33          | 28            | 111              |

- Example: to recover external decimal values converted to extended internal format and back to decimal,

- Extended hex float faithfully represents 32 decimal digits

- Extended binary float faithfully represents 33 decimal digits

- FP(16,6) and FP(2,24) faithfully represent 6 decimal digits

"OUT-IN" conversions: start with internal machine data, convert to external decimal, and back to internal

**OUT-IN Conversions**

| Precision | Binary<br>Digits | Hex<br>Digits | Decimal<br>Digits |

|-----------|------------------|---------------|-------------------|

| short     | 24               | 6             | 9                 |

| long      | 53               | 14            | 17<br>18          |

| extended  | 113              | 28            | 35<br>36          |

- Example: to recover long internal float values converted to decimal and back,

- Long binary float requires 17 decimal digits for faithful representation

- Long hex float requires 18 decimal digits for faithful representation

- "Rule of Thumb": OUT-IN needs 3 more decimal digits than IN-OUT

**Consequences of Finite Range**

#### **Value Ranges**

- Let  $\Omega$  (or  $\Lambda$ ) designate the largest representable normalized floating point number ("MaxReal" or "Huge")

- Sometimes (carelessly) nicknamed "infinity"; but  $\Omega \neq \infty$ :

- $-\infty/2 = \infty$ , while  $\Omega/2$  is finite!

- ∞×0 is meaningless, while Ω×0 = 0!

- S/390 hex:  $\Omega$  = X'7FFF....FF'  $\approx$  7.2  $\times$  10+75

- Let  $\omega$  (or  $\lambda$ ) designate the smallest representable normalized floating point number ("MinReal" or "Tiny")

- S/390 hex:  $\omega = X'0010...00' \approx 5.4 \times 10^{-79}$

- Many systems have a range asymmetry:

- Some representable small numbers have reciprocals exceeding  $\Omega$

- S/390 hex: no representable inverse for any number ≤ X'02100000'

- Some representable large numbers have reciprocals less than ω

- IEEE binary: inverses of largest numbers underflow or are denormalized

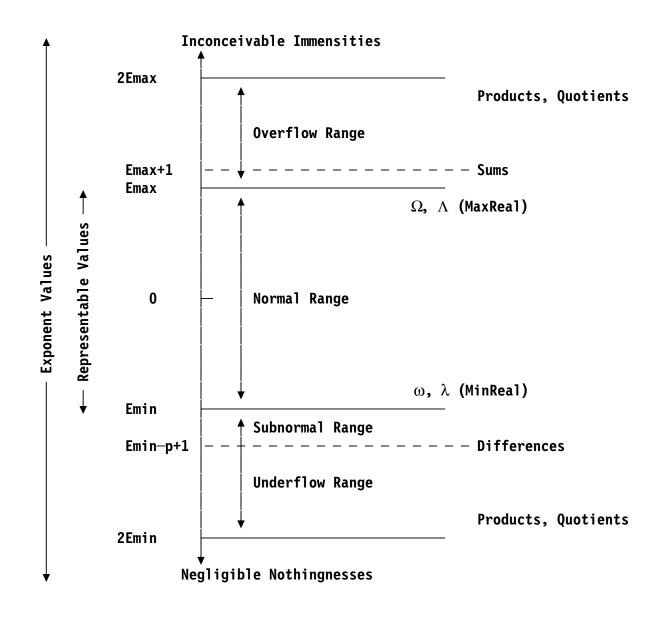

# **Exponent Range: Representable and Computable Values**

#### **Overflow and Underflow**

- Exponent range violations are called "overflow" and "underflow"

- Exponent >  $E_{max}$  = overflow

- Exponent <  $E_{min}$  = underflow

- Exponents of products and quotients of "normal" numbers can be nearly double the allowed exponent range

- Possible problems with directed rounding (e.g. IEEE):

- Numbers near  $\Omega^2$  (exponent near  $2E_{max}$ ) can be "rounded down" to  $\Omega$

- Numbers near  $\omega^2$  (exponent near  $2E_{min}$ ) can be "rounded up" to  $\omega$

- Sums of "normal" numbers can overflow E<sub>max</sub> by 1

- Differences of "normal" numbers can underflow E<sub>min</sub> by (p-1)

- May imply lost accuracy

- Various ways to handle these "subnormal" numbers

# **Handling Overflow and Underflow**

- Treatment (or mis-treatment) of range violations has pervasive impacts on programming

- Operations on overflowed values are difficult to manage

- The problems caused by range violations make ulps appear trifling...

- Range violations customarily handled by "fixups" of many types

- Overflows may be set to  $\Omega$ ,  $\omega$ ,  $\infty$ , or zero by various systems

- Underflows may be set to zero

- Overflows and underflows may return a finite value with modified characteristic (e.g. S/390 hex floating point interruptions "wrap" modulo 128)

- etc.

- Fixups may be done by hardware, software, or both

#### **Meaningless Computations**

- Programs may encounter pathologies: overflows, underflows, division by zero, square root of a negative argument, etc.

- Some machines respond with zero,  $\infty$ ,  $\Omega$ , others may provide explicit representations

- CDC: representations for ∞, "Indefinite," "Indeterminate" ("Not a Number")

- Arithmetic: NaN op any  $\to$  NaN; overflows  $\to \infty$ , underflows  $\to$  0; 0 ×  $\infty$   $\to$  NaN

- IBM Stretch: representations for ∞, infinitesimal (ε), OMZ ("Order of Magnitude Zero" with significand = 0)

- Arithmetic:  $\infty + x \rightarrow \infty$ ;  $\varepsilon + x \rightarrow x$ ; etc.

- System/360 significance exception has roots in OMZ

- DEC VAX: exponent = 0 and minus sign is a "reserved operand"

- Causes an interruption when accessed

Real-Mathematics Fictions,

Floating-Point Facts

"Everything You Know Is Wrong"

#### The Laws of "Real" Arithmetic

Closure The product (ab) and sum (a+b) of the real numbers

a and b are reals

Commutative (1) a+b = b+a, and (2) ab = ba

**Associative** (1) (a+b)+c = a+(b+c)

(2) (ab)c = a(bc)

**Distributive** a(b+c) = ab + ac

Units, Identities There are reals 0 and 1 such that

(1) a+0 = 0+a = a

(2)  $a \times 1 = 1 \times a = a$

**Inverses** For any real a

(1) There is a real -a with a+(-a) = (-a)+a = 0

(2) If  $a \neq 0$ , there is a real  $a^{-1}$  with  $a \times a^{-1} = a^{-1} \times a = 1$

#### • Consequences:

#### No Divisors of Zero

If ab = 0, then at least one of a or b must vanish

**Cancellation** If ab = ac and  $a \ne 0$ , then b=c.

**Subtraction** If (a-b) means a+(-b), then (a+b)-b = a

**Division** If  $b \neq 0$ , and a/b means  $ab^{-1}$ , then b(a/b) = a

- Inequalities

- 1. If a < b, then for all c, a+c < b+c

- **2.** If a < b and c < d, then a + c < b + d

- **3.** If b < c, and a is positive, then ab < ac

#### Real vs. Realistic (Floating Point) Arithmetic

- The "laws of real arithmetic" hold only approximately (or not at all)

- For most cases, it's pretty close

- But: you should always know where the problems will occur

- Small and large problems lurk everywhere

- Let FP(r,p) be a floating point system with radix r and precision p:

- FP(r,p,Round) means arithmetic in FP(r,p) is calculated to full precision and then is rounded

- FP(r,p,Chop) means arithmetic in FP(r,p) is calculated to full precision and then is chopped

- FP(r,p,ChopG) means arithmetic in FP(r,p) is calculated to at least (p+1) digits (at least one guard digit is used), and then is chopped (e.g., IBM Hex)

- FP(r,p,Chop0) means arithmetic in FP(r,p) is calculated with p digits (no guard digits are used), and then is chopped

#### **Floating Point Arithmetic Considerations**

- Full precision means "as though it's infinite precision" before rounding or chopping

- Full precision (rounded or chopped) arithmetic can be safely approximated with finite, fixed-length registers, plus

- One "Guard Digit"

- One "Rounding Digit" (if rounding is desired)

- One "Sticky Digit" (for both rounding and chopping)

- Costs of "doing it right" are reasonable today

- Costs of "doing it fast" still involve trade-offs

#### **Closure**

"The product (ab) and sum (a+b) of the floating-point numbers a and b":

**Fact**: they may not exist in FP(r,p)

Example: Overflow and underflow

Example: IBM Hex (FP(16,6)) contains 84357.0 and 0.84375, but not their sum, difference, quotient, or product.

#### **Commutative**

"(1) a+b = b+a, and (2) ab = ba":

Fact: true for almost all floating point systems

Example: ab ≠ ba on the Cray-1

The Cray-1 traded commutativity for speed

#### **Associative**

"(1) (a+b)+c = a+(b+c), and (2) (ab)c = a(bc)":

Fact: both fail to hold

(1) If a, b, and c have the same sign, then the results differ by at most

- 1 ulp, in FP(r,p,Chop) and FP(r,p,ChopG)

- r ulps, in FP(r,p,Round)

- (2) The results differ by at most

- r ulps, in FP(r,p,Chop) and FP(r,p,ChopG)

#### **Distributive**

a(b+c) = ab + ac:

Fact: fails to hold

If b and c have the same sign, then the results differ by at most

• r ulps, in FP(r,p,Chop) and FP(r,p,ChopG)

#### **Units**

"There are floating-point numbers 0 and 1 such that

$$(1) a+0 = 0+a = a,$$

Fact: true for many systems (but underflow may intrude)

(2)

$$a \times 1 = 1 \times a = a$$

":

Fact: true for <u>almost</u> all systems; fails in FP(r,p,Chop0)

#### Examples:

- The multiplicative identity (1×a=a) failed on the original IBM System/360 in long arithmetic (until corrected by IFPEC, the "Improved Floating Point Engineering Change") due to the lack of a guard digit.

- No guard digit on Cray, CYBER, Univac

Fact: May not be true for special values (e.g. "Not a Number")

#### **Inverses**

"For any floating-point number a

(1) There is a real -a with a+(-a) = (-a)+a = 0":

Fact: true in all known systems

"(2) If  $a \ne 0$ , there is a floating-point number  $a^{-1}$  with  $a \times a^{-1} = a^{-1} \times a = 1$ ":

Fact: fails to hold in many systems.

There may be no representable inverses

S/390 hexadecimal floating point has no representable inverse for any magnitude  $\leq$  X'02100000' (16<sup>-63</sup>)

#### **Inverses (continued)**

• Several a's may have the same  $a^{-1}$  (=1÷a)

Example: if r > 2, a number with fraction  $(1-r^{-p})$  has r-1 inverses in FP(r,p) with chopped arithmetic, and approximately (r-1)/2 inverses with rounded arithmetic

Example: In S/390 hexadecimal floating point,  $a^{-1}=b^{-1}$  means only that a and b may differ by 16 ulps.

Some a<sup>-1</sup> values give a×a<sup>-1</sup> ≠ 1

Example: In S/390 hexadecimal floating point, numbers with fraction  $(1-n\times r^{-p})$  have inverse  $r^{-1}$  if  $1\le n\le 15$

- Multiplying any fraction by a power of the radix leaves the fraction unchanged, except in FP(r,p,Chop0)

- This was a serious problem with the original System/360 long hex float

Example: In S/390 hexadecimal floating point,  $a \times (1/a)$  may differ from 1 by 16 ulps.

## The Facts of Floating Point Arithmetic: Consequences

#### No Divisors of Zero

"If ab = 0, then at least one of a, b must vanish":

Fact: frequently fails if overflow or underflow occurs

#### **Cancellation**

"If ab = ac and  $a \neq 0$ , then b=c":

Fact: b and c can differ by at most

- r-1 ulps, in FP(r,p,ChopG)

- r ulps, in FP(r,p,Round)

## The Facts of Floating Point Arithmetic: Consequences ...

#### **Subtraction**

"If

$$(a-b) = a + (-b)$$

, then  $(a+b)-b = a$ ":

**Fact**: frequently fails near underflow threshholds, or if |b| greatly exceeds |a|

- If (a+b) underflows to zero, then (a+b)-b = -b!

- If |b| is much larger than |a|, then (a+b)-b = 0!

Subtractions can easily lose significant digits

#### **Division**

"If  $b \neq 0$ , and a/b means  $ab^{-1}$ , then b(a/b) = a":

Fact: fails to hold

If b(a/b) = c, then |a| and |c| can differ by at most

• r ulps, in FP(r,p,ChopG)

## The Facts of Floating Point Arithmetic: Inequalities

1. "If a < b, then for all c, a+c < b+c":

Fact:

$$a+c \le b+c$$

**2.** "If a < b and c < d, then a + c < b + d":

Fact:

$$a + c \le b + d$$

**3.** "If b < c, and a is positive, then ab < ac":

Fact:

$$ab \le ac$$

- Strict mathematical inequalities must be weakened to tolerate equality in floating point systems

- Inequalities do <u>not</u> persist across floating point operations!

- The fact that equalities don't persist is better known

- Some floating tests for equality are simply bitwise comparisons

## Floating Point Pecularities and Pathologies

The following oddities have happened on widely-used machines:

- Some numbers have no inverse

- a has an inverse, but  $a \times a^{-1} \neq 1$

- z = y but  $z-t \neq y-t$

- $1/3 \neq 9/27$

- $y \times z \neq z \times y$ ;

- $z \neq 1 \times z \neq 0$ ;

- $\bullet \quad X + y \neq y + X$

- $2 \times y \neq y + y$

- $1 \times y \neq y$

- $0.5 \times y \neq y / 2$

## Floating Point Pecularities and Pathologies ...

- $((y \times z)/y)/z < .00001$  (caused by overflow to  $\Omega$ )

- $((y \times z)/y)/z > 100000$ . (caused by overflow to  $\omega$ )

- y>1>z>0 but y/z=0 (caused by overflow to 0)

- y/z < 0.99 but y-z = 0 (caused by underflow to 0)

- |z|<1, but the machine claims |z|≥1</li>

- The expressions x<y and x-y<0 are exactly equivalent on some computers but not on others.

- Some machines have different over/underflow threshholds for multiplication and/or division than for addition and/or subtraction.

- Some machines treat all sufficiently tiny nonzero numbers z as if they were zero during multiplication and division, but not during addition or subtraction.

#### Why Does Floating Point Work At All?

- 1. It closely approximates the way most of us do calculations (most of the time)

- 2. It handles most of the "dirty work" automatically

- 3. "The secret of success of floating-point computation lies in the fact that we continue to do arithmetic to **p** digits of precision even though the accuracy of our intermediate results has degraded so that we can only guarantee that a few digits are significant." (Sterbenz, p. 78)

#### **Some General Conclusions**

- You must "think floating point"

- And not "think real": real numbers are merely a pleasant abstraction

- Algebraic relations are <u>not</u> computational relations!

- 2. Small radix r means ...

- Relative error grows more slowly

- Post-normalization is needed more frequently

- More exponent bits needed for a given exponent range

- Example: binary requires 2 more exponent bits than hex for same range

- 3. Rounding in preference to chopping means ...

- Magnitude of average error tends to be smaller

- Arithmetic operations may require extra cycles

- 4. Always bear in mind *Murphy's Law of Floating Point*.

Anything that can go wrong, does on some computer.

# A Review of IBM Hex Floating Point

## **IBM Hex Floating Point**

Three radix-16 representations:

1. Short precision: 6 hex digits (not 24 bits!)

2. Long precision: 14 hex digits

3. Extended precision: 28 hex digits (fraction is in two parts)

| Single<br>(32—bit)<br>Format    | 1 7     | 24       |            |

|---------------------------------|---------|----------|------------|

|                                 | s char  | fraction |            |

| Double                          | 1 7     |          | 56         |

| (64-bit)<br>Format              | s char  |          | fraction   |

| Extended<br>(128—bit)<br>Format | 1 7     |          | 56         |

|                                 | s char  |          | fraction.1 |

|                                 | / ///// |          | fraction.2 |

#### **IBM Hex Floating Point ...**

- All representations have same exponent range

- 7-bit, base-16 exponent

- Exponent values: -64 to +63

- Magnitudes range from  $5.4\times10^{-79}$  to  $7.2\times10^{+75}$

- Unnormalized values permitted throughout exponent range

- Redundant representations for many values

```

Example: in short hex float, 1 = X'41100000', X'42010000', X'43001000', etc.

```

Example: X'nn000000' ("pseudo-zeros") treated as zero for all nn

- True zero has characteristic 00 (exponent = -64)

- Have effect only on addition and subtraction

- Multiplication and division are not affected, because the operands are pre-normalized internally (without causing exponent spills)

#### **IBM Hex Floating Point ...**

- Arithmetic truncates (usually, <u>but not always</u>, toward zero!)

- Example:  $1.0-16^{-7}=1.0$ , not  $1.0-16^{-6}$  (result not rounded toward zero)

- Example: X'42100000' X'40FFFFFF' = X'41F00001' (instead of X'41F00000'); result truncated <u>away</u> from zero, with error = 15/16 ulp.

- Square root is rounded

- Rounding isn't biased (source and target operands have same lengths)

- No reserved or special values

- Zero arithmetic results delivered as +0 ("true zero")

- Rounding modes previously only via "ACRITH" feature on 4361

- Now available on ESA/390

**IEEE Floating Point Standard**

**ANSI / IEEE Standard 754-1985**

"...meticulous attention to details that hardly matter to most people but matter, when they do matter, very much." (Kahan)

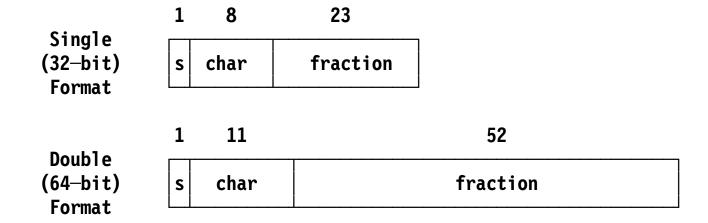

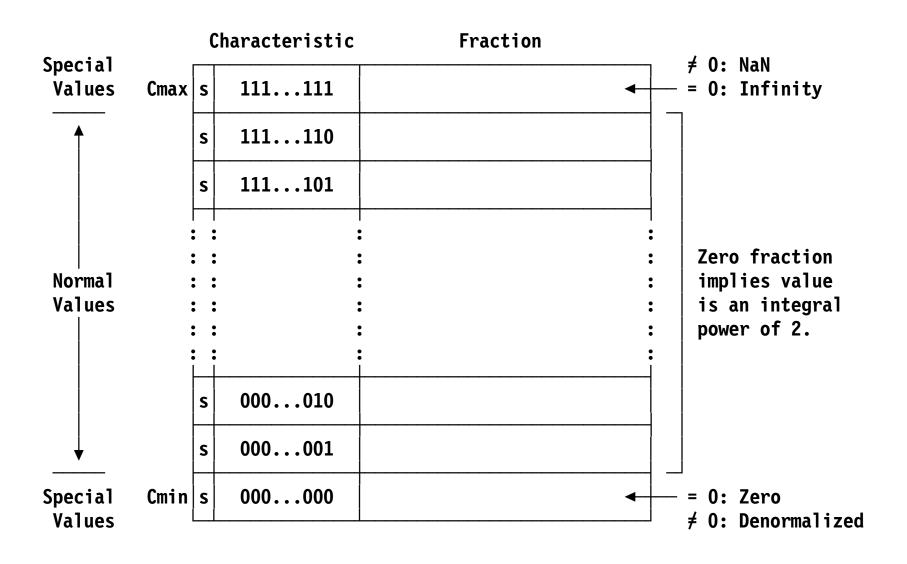

#### **IEEE Floating Point Standard: Representations**

- No redundant representations

- Two fully-defined <u>basic</u> formats: single and double precision

s: sign bit (0 = +, 1 = -)

char: characteristic ("biased exponent")

$C_{min} = 0$ ,  $C_{max} = all 1-bits$

fraction: has an extra <u>implied high-order 1-bit</u> for normal values;

significands therefore have 24-bit and 53-bit precisions

#### **IEEE Floating Point Standard: Normal Values**

| length | precision | <b>E</b> min | <b>E</b> <sub>max</sub> | bias  |

|--------|-----------|--------------|-------------------------|-------|

| single | 24        | <b>-126</b>  | +127                    | +127  |

| double | 53        | -1022        | +1023                   | +1023 |

- Exponent range: E<sub>min</sub> to E<sub>max</sub>

- Characteristic C = exponent e + bias

- Exponent's characteristic range:  $C_{min}+1$  to  $C_{max}-1$

- $C_{min}$  and  $C_{max}$  are reserved for special values (see slides 52-54)

- Significand = 1.fraction (leading 1-bit is implied)

- Fraction is therefore always normalized

- 1 ≤ significand < 2

## IEEE Floating Point Standard: Normal Values ...

#### Normal numbers

- Single precision (short) value:  $\pm$  (1.fraction)  $\times$  2<sup>char-127</sup>

- Magnitudes:  $1.175 \times 10^{-38}$  to  $3.403 \times 10^{+38}$

- Double precision (long) value:  $\pm$  (1.fraction)  $\times$  2<sup>char-1023</sup>

- Magnitudes:  $2.2231\times10^{-308}$  to  $1.7977\times10^{+308}$

#### Zero

- Characteristic =  $C_{min}$  (zero); fraction = 0

- Signed

- Examples of single precision values:

```

1.0 = B' 0 01111111 000......000 ' = X'3F800000'

15.0 = B' 0 10000010 1110000...000 ' = X'41700000'

0.1 = B' 0 01111011 10011001...011 ' = X'3DCCCCCD'

Max = B' 0 11111110 111......111 ' = X'7F7FFFFF'

Min = B' 0 00000001 000......000 ' = X'00800000'

-0.0 = B' 1 00000000 000......000 ' = X'80000000'

s <-char-> <-fraction->

```

#### **IEEE Floating Point Standard: Special Values**

- Designated by <u>reserved</u> characteristics C<sub>min</sub> (zero), C<sub>max</sub> (all 1-bits)

- Denormalized numbers

- Characteristic =  $C_{min}$  (zero)

- Fraction ≠ 0 (no implied "1." before the fraction)

- Value:  $\pm$  (0.fraction)  $\times$  2<sup>E</sup>min)

- Examples of single precision values:

```

1.0E-40 = B' 0 00000000 00...011000010 ' = X'000116C2'

Largest Denorm = B' 0 00000000 111......111 ' = X'007FFFFF'

Smallest Denorm = B' 0 00000000 000......001 ' = X'00000001'

s <-char-> <-fraction->

```

## IEEE Floating Point Standard: Special Values ...

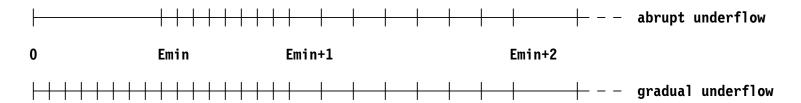

- Denormalized numbers allow "gradual underflow"

- Most helpful for addition and subtraction

- Can avoid many problems caused by "abrupt" underflows to zero

- (Y-X)+X gives X if underflow of (Y-X) causes abrupt "flush to zero"

- (Y-X)+X gives Y with denormalization (gradual underflow) of (Y-X)

- Abrupt underflow has no normal numbers smaller than E<sub>min</sub>

## IEEE Floating Point Standard: Special Values ...

- Infinity

- Characteristic = C<sub>max</sub> (all 1-bits); fraction = 0

- Signed

- Not-a-Number (NaN)

- Characteristic =  $C_{max}$  (all 1-bits); fraction  $\neq 0$

- Fraction value may be used by implementation to indicate specific conditions

- Two types are required: "quiet" (QNaN) and "signaling" (SNaN)

- Standard doesn't define distinct representations

- Sign is ignored ("not interpreted") in determining it's a NaN

- Examples of single precision values:

```

-Infinity = B' 1 11111111 0000....0000 ' = X'FF800000' a Quiet NaN = B' 0 11111111 1100....0000 ' = X'7FE00000' a Signaling NaN = B' 0 11111111 0100....0000 ' = X'7FA00000' s <-char-> <-fraction->

```

#### **IEEE Floating Point: Full Range of the Representation**

- Arithmetic operations

- add, subtract

- divide, multiply, remainder (which is very complicated!)

- compare (always exact; sign of zero is ignored)

- $-\pm 0$  are only two distinct IEEE bit patterns that compare equal

- Square Root

- Float/Integer conversions

- All supported float and integer formats inter-convertible

- Rounded float-to-integer conversion

- Conversions between float and decimal

- Decimal conversions assumed to be done in software

- Exceptions and exception handling rules

Conforming implementations must recognize five exception conditions:

## 1. Invalid operation

Mathematically meaningless operations

b.

$$\infty \times 0$$

C.

$$\infty \div \infty$$

$$d. 0 \div 0$$

e. x REM y with

$$x = \infty$$

or  $y = 0$

- f. SQRT(negative value)

- Computationally meaningless operations

- a. Operation on a Signaling NaN (SNaN)

- b. Relational operation involving a NaN ("un-ordered comparison")

- c. Integer-conversion fault (NaN, ∞, out of range)

#### 2. Division by zero

• N.B.: 0 ÷ 0 is an invalid operation

#### 3. Exponent overflow

## 4. Exponent underflow

Result may be denormalized

#### 5. Inexact result

May also occur coincident with overflow or underflow

Exceptions can trap, set a flag, or both

- Flags are required, traps are recommended

- Not all implementations support traps

- Non-trapped (masked, disabled) exceptions must set a flag

- Default: proceed without trap

- Trap and non-trap results may differ! (see slides 71, 113)

- Four rounding modes

- To nearest (the default; "ties" round to even); up; down; to zero ("chop")

- Integer conversions are subject to rounding mode

```

UP: +3.5 \longrightarrow +4, -3.5 \longrightarrow -3 DOWN: +3.5 \longrightarrow +3, -3.5 \longrightarrow -4 Toward Zero: +3.5 \longrightarrow +3, -3.5 \longrightarrow -3 To Nearest: \pm 3.5 \longrightarrow \pm 4, \pm 2.5 \longrightarrow \pm 2

```

- Remainder defined by  $r = x-y \times n$ , where n is the integer nearest the exact value of x/y; if |n-x/y| = 1/2, n is even

- Language rules may limit the choices

- E.g. C/C++ standard requires rounding "toward zero"

- ◆ Arithmetic rules require creation of -0 in some cases!

- SQRT(-0), X X (rounded down), (-0)+(-0)

- 0 remainder, 0 product, 0 quotient, 0 result of FIX

- E.g., (+2) REM (-1), (+0)×(-1), (+0)÷(-1), FIX(-0.2)

- E.g.,  $|A| \div (-\infty)$ , where A is finite

- Arithmetic on infinities is always "exact" and correctly signed

- If A is finite, then

$$A \pm \infty = \pm \infty$$

,  $|\infty| + |\infty| = \infty$ ,  $A \times \infty = \infty$ ,  $A \div \infty = 0$ ,  $A \div 0 = \infty$ , etc.

- Only exception condition recognized is "invalid operation" (e.g.,  $0 \times \infty$ ,  $\infty \div \infty$ ,  $|\infty| |\infty|$ , etc.)

- Overflow: default =  $\pm \infty$  or " $\pm$  MaxReal" depending on rounding mode

- Note potential problems in using MaxReal in subsequent computations!

- Single precision is <u>required</u> in all conforming implementations

- IEEE standard forbids double rounding in any operation

- "The result cannot suffer more than one rounding error"

#### **IEEE Floating Point Standard: Further Details**

- "Extended" Precisions are suggested

- Single Extended: at least 11 exponent bits, at least 32 fraction bits

- Most implementations use double for "single extended"

- Double Extended: at least 15 exponent bits, at least 64 fraction bits

- Implementations should support

- the extended format corresponding to the widest basic format supported

- mixed-length operations

- Relational Predicates for languages (20 suggested)

- Standard recommends implementation of many new relations to accommodate testing and comparing of NaNs

- Example: (A ?> B) is true if (A > B) or the relation is unordered

- NaNs have no ordering relationship to anything (including themselves)

- Example: (NaN eq NaN) is false, even if the NaNs are identical!

#### **IEEE Floating Point Standard: Recommended Functions**

- 1. COPYSIGN(x,y): returns x with sign of y, for any y

- 2. -x: is x copied with sign reversed (not 0-x)

- 3. SCALB(y,N): returns  $y \times 2^N$  for integral N

- 4. LOGB(x): returns unbiased exponent of x

- 5. NEXTAFTER(x,y): returns next representable neighbor of x in the direction of y

- 6. FINITE(x): returns TRUE if x is not an infinity or a NaN, FALSE otherwise

- 7. ISNAN(x): returns TRUE if x is a NaN

- 8. x<>y: is TRUE only when x<y or x>y

- 9. UNORDERED(x,y): returns TRUE if x is unordered with y

- 10. CLASS(x): tells which of ten classes x falls into:

- Signaling NaN; quiet NaN; —infinity; negative normalized nonzero; negative denormalized; —0; +0; positive denormalized; positive normalized nonzero; +infinity.

#### **IEEE Floating Point Standard: Justifications**

- 1. Facilitate program portability

- Easier exchange of programs and floating point data among systems

- Reproducible results (depending on the compiler, math library,...)

- 2. Enhance safety

- Fewer computational eccentricities to trap the unwary

- Reduce anomalous behavior to the inescapable minimum

- Minimize idiosyncrasies and programming contortions

- Simpler code is usually faster, cheaper, more robust

- 3. Reduce behavior unpredictability at precision and range threshholds

- 4. Minimize impact of wobbling precision

- 5. Enhance capabilities

- Better exception handling facilities

IEEE Standard 854 (1987) generalizes 754 to binary and decimal formats

Conformance to 754 gives conformance to 854

## ESA/390 Floating Point Enhancements

Web page:

http://www.ibm.com/s390/ieee/

#### **ESA/390 Floating Point Enhancements: Overview**

- Design goals include:

- Affordability

- Minimal impact to existing applications

- Serviceability

- Compatibility

- Definitive support

- Standard conformance

- ESA/390 supports both hexadecimal floating point (HFP) and IEEE binary floating point (BFP)

- Fully-conforming implementation of IEEE floating point standard for single and double precision

- Extended precision lacks only the remainder function!

- Precisely rounded decimal/binary conversions handled in software

- Easy migration from HFP, and to and from other platforms

- Software support in OS/390, HLASM, C/C++, LE, Java, UNIX System Services, etc.

## ESA/390 Hardware Enhancements

- New processor features

- Hexadecimal floating point extensions

- Floating point support instructions for HFP and BFP

- Binary (IEEE) floating point support

- Data types, exceptions, rounding modes, instructions

#### **ESA/390 Floating Point Enhancements: Processor Features**

- Extensions controlled by "AFPR" bit (CR0.13)

- 12 additional floating point registers (AFPR)

- 1, 3, 5, 7, 8 through 15

- pairing always between registers FPR<sub>n</sub> and FPR<sub>n+2</sub> (as before):

0-2, 1-3, 4-6, 5-7, 8-10, 9-11, 12-14, 13-15

- Usable by HFP <u>and</u> BFP operations

- Three new BFP data types

- Floating Point Control (FPC) register

- Data exception extended to store <u>Data Exception Code</u> (DXC)

- Locations 144-147

- Old "data exception" (Program Interruption Code 7) now called "decimal data exception" with zero DXC

- 121 new instructions for HFP, BFP and FP Support

- Five new instruction formats

#### ESA/390 Floating Point Enhancements: BFP Data Types

- Three data lengths

- Short (4 bytes) and long (8 bytes) same as IEEE-standard single and double

- Extended (16 bytes): 15-bit exponent, 112-bit fraction (113-bit significand)

- Magnitudes:  $3.4 \times 10^{-4392}$  to  $1.2 \times 10^{+4392}$

- Extra precision important for intermediate computations with long variables!

- Equivalent to "quad" format in HP PA-RISC, DEC Alpha, SUN SPARC

- BFP long and extended formats satisfy IEEE requirement for "Single Extended" and "Double Extended"

- Storage-operand lengths match register-operand lengths

- Helps avoid some optimization problems (see slide 124)

- Maximum and minimum normalized and denormalized values:

| Extreme Values | Short                 | Long                   | Extended                |

|----------------|-----------------------|------------------------|-------------------------|

| Max Norm       | 3.4×10 <sup>38</sup>  | 1.8×10 <sup>308</sup>  | 1.2×10 <sup>4932</sup>  |

| Min Norm       | 1.2×10 <sup>-38</sup> | 2.2×10 <sup>-308</sup> | 3.4×10 <sup>-4932</sup> |

| Min Denorm     | 1.4×10 <sup>-45</sup> | 4.9×10 <sup>-324</sup> | 6.5×10 <sup>-4966</sup> |

## ESA/390 Floating Point Enhancements: BFP Data Types ...

- Infinities (characteristic all 1-bits, zero fraction)

- NaNs (characteristic all 1-bits, non-zero fraction) (see slide 104 also)

- SNaN (Signaling NaN): leftmost fraction bit F0 = 0

- The rest of the fraction must have non-zero bit(s) (otherwise it's an infinity)

- Causes invalid-operation exception for almost all instructions

- QNaN (Quiet NaN): leftmost fraction bit F0 = 1

- Special "hardware" QNaN delivered as default for masked IEEE Invalid-operation exception: F0 = 1, rest of fraction = 0

- Delivered operands:

- SNaNs chosen over QNaNs

- NaNs of same type are chosen in order of operand number

- Six classes of floating point data (see "Test Data Class" instruction)

- Zero; normalized; denormalized; infinity; QNaN; SNaN

# **ESA/390 Floating Point Control Register**

| 8                 | 8                 | 8   | 8                |

|-------------------|-------------------|-----|------------------|

| IEEE<br>mask bits | IEEE<br>flag bits | DXC | Rounding<br>Mode |

Mask bits disable and enable IEEE exception "trap" conditions:

| <u>bit</u> | <u>Condition</u>       |

|------------|------------------------|

| 0          | IEEE invalid operation |

| 1          | IEEE divide by zero    |

| 2          | IEEE overflow          |

| 3          | IEEE underflow         |

| 4          | IEEE inexact result    |

| 5–7        | Reserved               |

- Flag Bits

- Same definitions as for mask bits

- Set on by masked exceptions; stay on until explicitly reset

- Masks and flags are ignored for HFP and FP Support instructions

## ESA/390 Floating Point Control Register ...

- Terminology: IEEE "trap" = S/390 "interruption"

- Actions on exception conditions:

- Mask bit = 1: set exception code in DXC field, take interruption

- Mask bit = 0: set flag bit in FPCR, take default action

- Note: results may differ between masked/unmasked exceptions:

- 1. **Invalid operation**: taking interruption suppresses the instruction

- add unlike infinities; subtract like infinities;  $0 \times \infty$ ; 0/0 or  $\infty/\infty$ ; (x REM y) with  $x = \infty$  or y = 0; SQRT(<0); Compare and Signal with QNaN; conversion fault: masked default = special "hardware" QNaN

- Signaling NaN: masked default = corresponding QNaN

- 2. Divide by 0: interrupt suppresses; masked default =  $\pm \infty$

- 3. **Underflow**: interrupt wraps exponent; masked default = denormalized result or zero

- 4. Overflow: interrupt wraps exponent; masked default = infinity or MaxReal

- 5. **Inexact result**: deliver rounded result (can also occur with BFP overflow or underflow)

# ESA/390 Floating Point Control Register ...

- DXC (Data Exception Code) indicates which exception/trap occurred

- 00 Decimal data exception

- Invalid AFPR used by HFP or BFP; FP-extensions hardware is installed, but CR0.13 bit = 0

- 02 BFP instruction; FP hardware installed, but CR0.13 bit = 0

- 08 IEEE inexact, result truncated

- 0C IEEE inexact, result incremented

- 10 IEEE underflow, exact result

- 18 IEEE underflow, result inexact and truncated

- 1C IEEE underflow, result inexact and incremented

- 20 IEEE overflow, exact result

- 28 IEEE overflow, result inexact and truncated

- 2C IEEE overflow, result inexact and incremented

- 40 IEEE division by zero

- 80 IEEE invalid operation

- Bits 0-4 match masks and flags;

bit 5 indicates inexact result was incremented in magnitude

## **ESA/390 Floating Point Enhancements: Rounding Modes**

- Rounding mode indicated in FPCR (bits 30-31):

- Unbiased round to nearest

- 1 Round toward zero (chop/truncate)

- **2** Round toward  $+ \infty$

- **3** Round toward  $-\infty$

- Some instructions can specify an explicit rounding-method mask field:

- 0 Round according to the current rounding mode in the FPCR

- 1 Biased round to nearest

- 4 Unbiased round to nearest

- **5** Round toward zero (chop)

- **6** Round toward  $+ \infty$

- **7** Round toward  $-\infty$

Used by Convert to Fixed, Load FP Integer, Divide to Integer instructions

#### **ESA/390 HFP Enhancements**

- Previous hex floating point exceptions and Program Mask bits renamed with "HFP" prefix

- E.g. "Exponent overflow" becomes "HFP exponent overflow"

- 26 new instructions (54 previously available)

- Convert from fixed (all 3 precisions; round toward zero)

- Convert to fixed (all 3 precisions, <u>with</u> selectable rounding)

- Load FP integer (rounded toward zero, HFP result; all 3 precisions)

- Extended-precision ops (similar to existing short and long ops)

- LTXR, LCXR, LNXR, LPXR (rectify low-order sign and characteristic)

- CXR, SQXR

- LEXR (does biased round, like LRER, LRDR)

- Multiply short  $\times$  short to yield short (MEE, MEER)

- Square root for short and long storage operands (SQE, SQD)

- Load lengthened (eliminates need to clear registers first)

- LDE(R), LXE(R), LXD(R)

# **ESA/390 Floating Point Support Instructions**

- 8 new instructions

- 3 Load Zero, 1 Load Extended, 4 BFP-to-HFP, HFP-to-BFP conversion

- None cause any HFP or IEEE-defined exceptions

- CC=3 for "special case" results (may get MIN, MAX, or ∞)

- Load zero (HFP and BFP, for all three operand lengths)

LZXR FO Zero FO/F2 (old HFP code required two instructions)

- Subtracting a register from itself can cause IEEE exceptions!

...or HFP Significance exception if not masked off!

- Load extended (LXR, register-register): replaces 2 LDRs

## ESA/390 Floating Point Support Instructions ...

- Conversions between BFP and HFP replace 30+ instructions with one!

- Convert HFP to BFP (long HFP to short or long BFP)

```

TBDR F2,RM,F3 Convert long HFP in F3 to long BFP in F2 TBEDR F9,RM,F1 Convert long HFP in F1 to short BFP in F9

```

- Note: rounding modifier RM=0 means "round toward zero,"

not "according to current rounding mode"

- Convert BFP to HFP (short or long BFP to long HFP)

```

THDER F0,F1 Convert short BFP in F1 to long BFP in F0 THDR F12,F5 Convert long BFP in F5 to long BFP in F12

```

- Note: no rounding modifier!

- Exceeding range gives 0 or ± HexMax

- 87 new instructions (almost all mnemonics contain a 'B')

- Actions are more complex than HFP equivalents, due to

- rounding modes

- NaNs and infinities

- maskable exceptions

- different exponent ranges

- Full range of usual operations

- Add, subtract, multiply, divide, square root

- Multiply includes short  $\times$  short = long, long  $\times$  long = extended

- NaN op NaN gives 1st operand

- Load, Load Complement/Negative/Positive

- These don't signal invalid operation with SNaN operands!

- Load Complement implements IEEE recommended function -x (see slide 62)

- CC = 3 generally indicates NaN operand or result (no CC = 3 for HFP ops)

- No unnormalized data (or unnormalizing arithmetic operations)

- Denormalized numbers are default result of underflow

- BFP Comparisons (HFP instructions unchanged)

- Normal compare:

CEBR F1,F9 Compare long float values in F1, F9

- Invalid operation signaled if at least one operand is a SNaN

- CC=3 for comparisons involving QNaNs ("unordered")

- Note: CC=3 setting is new with BFP compare instructions

- Compare and Signal: like Compare, but <u>all</u> NaNs signal Invalid Op

KEBR F1,F9 Compare long float values in F1, F9, signal all NaNs

- Sets CC=3 for comparisons involving any NaN

- Comparing mixed-length operands requires lengthening the shorter

- Implements recommended IEEE functions <>, UNORDERED (see slide 62)

- Convert to 32-bit fixed-point binary integer from float

- Previous HFP code to convert long float in F0 to integer in R0:

```

AD 0,DCON Add and normalize

STD 0,FTEMP Store the intermediate sum

L 0,FTEMP+4 Get the integer result in R0

---

FTEMP DS D Doubleword temporary

DCON DC X'4F08 0000 0000 0000' Conversion constant

```

- 3 instructions and 3 storage references

- New HFP and BFP code to do the same (note rounding-mode mask!):

```

CFDR RO,RM,FO HFP to Integer

CFDBR RO,RM,FO BFP to Integer

```

- 1 instruction and <u>no</u> storage references!

- Convert to fixed supports rounding mask field

- If invalid operation and mask bit = 0, sets CC = 3

- Convert from 32-bit fixed-point binary integer to float

- Previous HFP code to convert integer in R0 to long float in F0:

```

X

0.DCON+4

Invert sign bit of integer

0,FLOAT+4

Store result in long constant

Load the unnormalized value

0,FLOAT

O.DCON

Add and normalize

AD

DCON

DC

X'CE00 0000 8000 0000'

-2**31

X'4E00 0000 0000 0000'

FLOAT DC

Pseudo-zero, Exponent = +14

```

- 4 instructions and 4 storage references

- New HFP and BFP code to do the same:

```

CDFR F0,R0 Integer to HFP

CDFBR F0,R0 Integer to BFP

```

- 1 instruction and <u>no</u> storage references!

- CC unchanged; rounding according to current rounding mode

- Load and Test, Load Lengthened

- BFP Load and Test sets CC=3 is result is a NaN

- HFP Load and Test instructions never set CC=3

- New "lengthening" instructions for HFP and BFP:

```

LDER r1,r2 HFP short to long

LXDR r1,r2 HFP long to extended

LXER r1,r2 HFP short to extended

LDEBR r1,r2 BFP short to long

LXDBR r1,r2 BFP long to extended

LXEBR r1,r2 BFP short to extended

```

- Condition code is unchanged

- Invalid operation signaled if operand is SNaN

- NaNs extended with trailing zeros, shortened by truncating on the right

- Stable encoding of special values in NaNs must use leftmost bits

- Previous HFP code to lengthen a short float:

```

SDR F0,F0 Clear FPReg 0

LE F0,X Load the short float; F0 now has long value

```

- Load FP Integer (rounds FP operand to FP integer value)

- Previous HFP code for integer part of long float in F0:

AD F0,=X'4F00 0000 0000 0000' Force fraction part off

New HFP and BFP code to do the same:

FIDR F0,F0 HFP integer part of F0 FIDBR F0,R0 BFP integer part of F0

- CC is unchanged

- Load rounded (long or extended to short, long to short)

- Three new HFP instructions added (LEDR, LDXR, LEXR)

- Alternate mnemonics for existing ops: LEDR = old LRER, LDXR = old LRDR

- Exponent overflow possible only if operand = HFP MaxReal

- BFP operations (LEDBR, LDXBR, LEXBR) must account for exponent width reduction

- Possible exceptions: Overflow, Underflow, Inexact, Invalid Op

- Rounding controlled by current rounding mode

- Divide to integer

- Produces 2 BFP results: integer quotient, exact (rounded) remainder

- Similar to MOD/modulo, but not the same!

- May need re-execution to complete

- CC setting indicates status of calculation

- Example: calculate remainder of 1000/0.73 using short BFP:

```

LE F8,=EB'1000' Set up dividend

LE F3,=EB'0.73' Set up divisor

DIV FIEBR F8,F3,F0,RM Partial quotient in F0, partial remainder in F8

BC 2,DIV Iterate if not complete

--- Final remainder in F8

```

- Rounding modifier RM selects rounding mode

- HFP (long precision) code for remainder of 1000/0.73:

```

LD F0,=D'1000' Get numerator (A)

DD F0,=D'0.73' Compute quotient (A/B)

AD F0,=X'4F00 0000 0000 0000' Force fraction part off

MD F0,=D'0.73' Compute (B * IntegerPart(A/B))

LCDR F0,F0 Complement

AD F0,=D'1000' A - (B * Int(A/B)) is the remainder in F0

```

- Multiply-and-add, Multiply-and-subtract (short and long)

- op1 = op3  $\times$  op2  $\pm$  op1, with precise intermediate result

- Only the <u>final</u> result is rounded (possibly non-standard result!)

- Result NaN taken from operand in order op3, op2, op1

- SNaN defaulted to QNaN takes precedence

- Consistent with the same operations on RS/6000

Test Data Class: bit pattern of second operand address selects first-operand class(es) to be tested

| Class    | + sign | - sign |

|----------|--------|--------|

| Zero     | 20     | 21     |

| Norm     | 22     | 23     |

| Denorm   | 24     | 25     |

| Infinity | 26     | 27     |

| QNaN     | 28     | 29     |

| SNaN     | 30     | 31     |

- Match of mask bit to operand class sets CC=1

- No invalid-operation signal for SNaNs (so you can test for them!)

- 12-bit pattern fits in instruction's displacement field

- Implements recommended IEEE functions FINITE, ISNAN, CLASS (see slide 62)

# **ESA/390 Floating Point Enhancements: Control Instructions**

FPCR Load/Store (register-storage), Set/Extract (register-register)

```

SFPC R1 Set FPCR from GPR 1

EFPC R1 Extract FPCR into GPR 1

LFPC D2(B2) Load FPCR from memory

STFPC D2(B2) Store FPCR into memory

```

Set Rounding Mode: rightmost two bits of 2nd-operand address

```

SRNM 0(R5) Set rounding mode from bits 30-31 of GPR 5

SRNM 1 Set rounding mode to 'toward zero'

```

# **ESA/390 Software Enhancements**

- OS/390 support

- High Level Assembler support

- C/C++ support, including LE and runtime libraries

- Considerations for Java, DB2, CICS, IMS, other products

- Programming conventions

## **OS/390 Operating System Support**

- Delivered with OS/390 V2R6

- Can emulate FP Extensions on older hardware; useful for testing, development, validation

- Task initiation

- TCB or SRB not initially enabled for BFP ops or AFPR, FPCR

- First exception is trapped:

- If FP-extensions hardware is installed, turn on CR0.13, enable register saving

- May want to use AFPRs for HFP only

- If DAT on and no hardware, simulate instructions and enable register saving

- Registers initialized to zero for new tasks

- FPCR = 0 disables traps, resets flags, sets rounding mode to "nearest"

- XCTL, LINK, LOAD-and-CALL: callee gets caller's registers

- LE enclaves: LINK requires special initialization handling

- IEAFP service call to stop saving/restoring registers

- Can reduce task-switching overheads

# OS/390 Operating System Support ...

## Exceptions:

- DXC = 0 for old decimal data exception (Program Interruption Code 7)

- DXC passed in parm area to ESPIE, ESTAE, FRRs

- SPIE must use DXC in FPCR

#### Two CVT bits:

- CVTBFP (in CVTOSLV2): you can use FP Extensions (may be emulated)

- CVTBFPH (in CVTFLAG2): the FP Extensions hardware is present

- Sysplex: WLM directs jobs to BFP-capable systems

- UNIX System Services: enhancements to fork(), exec(), spawn(), ptrace(), pthread\_create(), and od command

# **ESA/390 Floating Point: HLASM Support**

- Delivered with High Level Assembler R3

- Fully compatible with existing HFP instructions and data

- All new HFP, BFP and FP Support instructions

- Extend DC syntax of E/D/L-type constants for BFP data:

- m = 1 for biased round to nearest; m = 4, 5, 6, 7 have same meanings as rounding-modifier masks (see slide 73)

- Default is R4 ("round to nearest")

# ESA/390 Floating Point: HLASM Support ...

Signed zeros supported

```

NegZero DC EB'-0' generates X'80000000' DC EH'-0' generates X'80000000' 01dZero DC E'-0' generates X'00000000'

```

Examples of BFP conversions:

```

Short1

EB'1.0'

DC

generates X'3F800000'

Long10th DC

DB'0.1'

generates X'3FB99999 9999999A'

Tenth

EB'0.1'

generates X'3DCCCCCD' (rounded to nearest)

DC.

DC

EB'0.1R5'

generates X'3DCCCCCC' (rounded toward zero)

ExtBia

DC

LB'1.5E4000' generates X'73E73A97 C4B5FD80 5291940A C3F3C992'

```

- Minimum bit-length modifiers are 9, 12, 16 for E, D, and L

- No fraction bits remain at minimum bit length

# ESA/390 Floating Point: HLASM Support ...

#### Extreme values:

- Nominal values may be (MAX) and (MIN)

- (MIN) is the minimum <u>normalized</u> value

- Minimum denormalized value = X'000...001'

### Special values:

- Nominal values may be (SNAN), (QNAN), (NAN), (INF)

- Leading fraction bits for NaNs: 01 for (SNaN), 11 for (QNaN), 10 for (NaN) (the special "hardware" QNaN) (see slide 69)

- Minimum bit lengths for NaNs: 11, 14, 18 for E, D, and L

#### Examples:

```

EB'(Min)'

ShortMin DC

generates X'00800000'

EB'(Inf)'

generates X'7F800000'

ShortInf DC

LongSNaN DC

DB'(SNaN)'

generates X'7FF40000 00000000'

LB'(Max)'

ExtMax

DC

LongDMin DC

XL8'1'

generates X'0000000 00000001'

```

"Parameterized" NaNs discussed at slide 104

# ESA/390 Floating Point: HLASM Support ...

Improved and directed rounding supported for HFP data also:

- Existing HLASM float hex conversions are <u>very</u> good;

but "difficult numbers" require more highly precise conversions

- Examples:

```

DC D'.303325544866797714604E-10' generates X'382159DA E5B7B6BD' (old) DC DH'.303325544866797714604E-10' generates X'382159DA E5B7B6BE' (new) DC D'.185240322463448422373E-23' generates X'2D23D4A8 0F402692' (old) DC DH'.185240322463448422373E-23' generates X'2D23D4A8 0F402693' (new)

```

# **ESA/390 Floating Point: HLASM Toolkit Feature Support**

- All new HFP, BFP and FP Support instructions supported by

- Interactive Debug Facility

- New AFPR command to enable display of FPCR, AFP registers

- Disassembler

- Program Understanding tool

# **C/C++ Compiler Support**

- OS/390 V2R6 required (compiler uses some runtime library routines)

- BFP instructions not used at compile time

- No support for mixing binary/hex floating point in one compilation unit

- Emphasis is on BFP

- Assumption: mixed-mode applications rare

- Supported... but the user is responsible for managing the mixtures!

- Many new or changed options:

```

arch(3)

OK to use AFPR, all new instructions

float([no] afp)

Selects whether or not to use AFPR

float(ieee | hex)

Selects float mode

```

# C/C++ Compiler Support ...

float([no]fold)

OK to evaluate constant expressions at compile time

round (N|M|P|Z)

Determines compile-time rounding of constant expressions

float([no]rrm)

rrm means runtime changes to rounding mode; compiler restricts some optimizations

[no]strict

Restrict compiler optimizations so results are determinable and repeatable; nostrict relaxes conformance to IEEE rules and allows some reorderings for performance gains

float([no]maf)

maf means OK to use multiply-and-add, multiply-and-subtract ops

- Strictly-compliant code generated when strict, nomaf specified

- If nostrict and float(ieee), get maf

## **C/C++ and LE Runtime Library Support**

- Library functions include routines

- To perform correctly rounded decimal/float conversions

- Uses same algorithms as HLASM

- For users who <u>must</u> manage mixed floating point modes during execution:

- Return FP mode of compilation unit

- Override FP mode of compilation unit

- Query and set fields of FPCR

- Determine available hardware and operating system support

- Convert between HFP and BFP

- ... and others, documented in the LE Vendor Interface book

- Other functions are documented on the LE web site

- Math functions: Sun's "Freely Distributed Math Library" (fdlibm)

- Long (64-bit) precision only

- Default rounding mode only

## C/C++ and LE Runtime Library Support ...

- Class library support for BFP packaged in DLLs

- Assumption: one copy of the DLL will be shared by all applications

- Feature-test macro and name-mangling rules distinguish BFP/HFP routines

- Language Environment

- Runtime routines can handle modules with different FP modes.

- PPA2 has FP mode flag bit

- Routines sensitive to mode (like printf, scanf) test it to process data in mode of compilation unit

- Assembler macros can set PPA2 flag to indicate BFP is used

- LE enclave initiation saves creator's non-volatile FPRs, sets FPCR = 0 (restored on enclave termination)

- Supports BFP exceptions, AFPR for BFP and HFP exceptions

- Signal catchers get control with BFP exceptions disabled (FPCR saved/restored by runtime)

- Dump formats FPCR and AFPR

#### **Java Language Definition**

- Symbolics for INF, NAN, MAX, MIN (=DMIN; no NMIN)

- Casting functions for bits-to-float

- Relationals with NaNs return false (not "unordered": x != x is true for NaNs)

- Only rounding mode is "to nearest"

- Overflows give ∞, underflows give zero

- Integer-to-float conversions give no indication of lost bits

- Float-to-integer conversions:

- NaN gives 0

- Representable values round to zero (truncate)

- Non-representable values (including ∞) give MAXINT or MININT (no exceptions indicated)

- Double-to-float rounded to nearest, or to 0 or ∞ (no exceptions indicated)

- Coalesces all NaN values to "a single conceptual NaN value"

- Java's support of the IEEE standard is (currently) somewhat limited...

## **Java Support: Implementations**

- Improved performance for (previously emulating) applications

- Java Virtual Machine (JVM) on OS/390 V2R6 and new hardware will generate BFP instructions

- Uses C/C++ runtime library

- Old hardware: use Java Runtime Library IEEE simulation

- Just-In-Time (JIT) compiler on OS/390 V2R6 and new hardware will generate BFP instructions

- Old hardware: use Java Runtime Library IEEE simulation

- High-Performance Java (HPJ) compiler R1 uses IEEE simulation

- March 1999 PTF provides AFPR and BFP-instruction support

#### **Other Products' Support**

- VS Fortran:

- AFPR support for HFP (APAR PQ26305)

- DB2 UDB for OS/390

- Phased approach to support, over several releases

- Initially: BFP converted to HFP internally

- Don't use BFP data until "Toleration PTFs" (APARs PQ30062, PQ30063) are applied

- Utilization of new instructions will require compatibility testing

- A new data type and related capabilities will be considered

- CICS

- Transaction Server currently does not support BFP applications;

Open Transaction Environment tasks can use BFP

- IMS is "transparent" to floating point data types

- DFSORT intends to provide BFP support equivalent to HFP

- Component Broker intends BFP support in the future

- TCP/IP intends to add support to RPC for BFP

# **ESA/390 Floating Point Software Conventions**

- Old floating point register convention: <u>all</u> FPRs volatile

- Too few FPRs to justify optimizing contents across calls

- Now: FPRs 0-7 volatile; 8-15 saved and restored across calls

- Called routine must save modified non-volatile FP registers

- Allows optimization of variables into registers across calls

- No impact on programs using old conventions for FPRs 0-6

# ESA/390 Floating Point Software Conventions ...

- Floating Point Control register

- Volatile: need not save/restore exception flags, DXC

- Non-volatile: must save/restore masks, rounding mode

- Application is responsible for knowing what data types are used

- Assumption: rarely intermix HFP and BFP data types

- Asynchronous exits must preserve FPRs, FPCR

- BAKR, PC calls get caller's FPRs and FPCR

- Not saved on linkage stack

# ESA/390 Floating Point Software Conventions ...

- Standard: "NaNs should ... afford retrospective diagnostic information inherited from invalid or unavailable data and results."

- Potential value in "tagging" or "parameterizing" NaNs

- Can distinguish/describe many types of error or warning conditions

- Propagation of NaNs helps identify initial error condition

- NaN representations and parameterizations

- Recommend reserving the <u>two</u> high-order fraction bits

- **O1** SNaN (rest of fraction = 0)

- **10** Hardware-generated default QNaN (rest of fraction = 0)

- 11 Software-created default QNaN (rest of fraction = 0)

- Recommend using <u>at most</u> 21 high-order bits for NaN parameter values

- Longer fields may suffer truncation

- Discussion question: Should we reserve the high-order bit of this 21-bit field to distinguish between IBM/user "tagging" info?

# Contrasting Binary and Hexadecimal Floating Point on ESA/390

# **Binary and Hex Floating Point: General Differences**

Summary of HFP and BFP data formats

| Format          | sign<br>width | characteristic<br>width | characteristic<br>bias | fraction<br>width |

|-----------------|---------------|-------------------------|------------------------|-------------------|

| Hex Short       | 1             | 7                       | 64                     | 24                |

| Hex Long        | 1             | 7                       | 64                     | 56                |

| Hex Extended    | 1             | 7                       | 64                     | 112               |

| Binary Short    | 1             | 8                       | 127                    | 24                |

| Binary Long     | 1             | 11                      | 1023                   | 53                |

| Binary Extended | 1             | 15                      | 16383                  | 113               |

# Binary and Hex Floating Point: General Differences ...

- 1. Range: Significant differences

- Short IEEE binary has half the range of short S/390 hex

- Double IEEE binary has four times the range of long S/390 hex

- Extended IEEE binary has 64 times the range of extended S/390 hex

- 2. Precision: Minor differences

- Short IEEE binary has 0 to 3 more fraction bits than short S/390 hex

- Long IEEE binary has 0 to 3 fewer fraction bits than long S/390 hex

- Extended IEEE binary has 1 to 4 more fraction bits than extended S/390 hex

- 3. Special values: Significant differences

- S/390 hex has no representation for NaNs or infinities

- 4. Unnormalized/denormalized values: Important differences

- S/390 hex supports (but rarely produces) unnormalized data

- IEEE denorms can indicate "lost" precision

# **Binary and Hex Floating Point: Representation Differences**

- A 24-bit binary fraction is *not* the same as a 6-hex-digit fraction!

- Computationally: 6 hex digits "statistically equivalent" to approximately 22 bits

- Example: consider the decimal value 0.1

- In binary: 0.0001 1001 1001 1001 1001 1001 1001 ... etc.

- Short hex-normalized float fraction has 21 significant bits:

- Normalized, rounded fraction is X'19999A' (relative error  $\approx 2^{-22}$ )

- Stored value is X'4019999A'

- Single precision IEEE float fraction has 24 significant bits:

- Normalized, rounded fraction is X'CCCCD' (relative error  $\approx 2^{-25}$ )

- With the implied 1-bit, stored value is

B'0 01111011 1001100110011001101' or X'3DCCCCCD'